LDr,(HL)

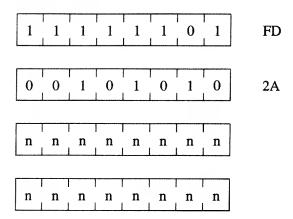

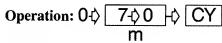

SRA m

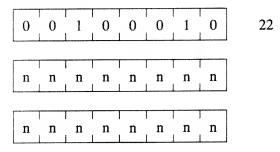

ADD A, r

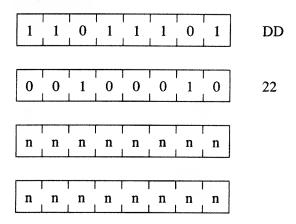

IFee TRUE, PC ↓ nn

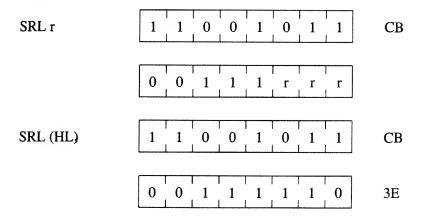

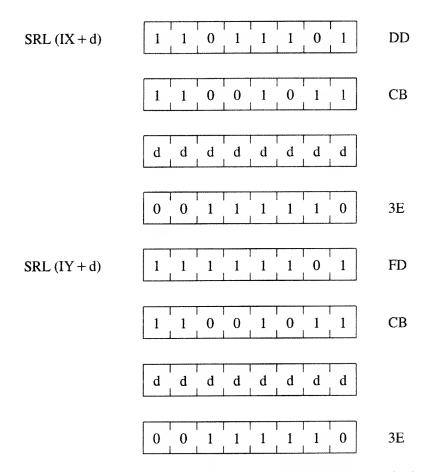

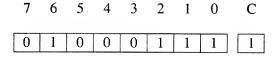

SRL m

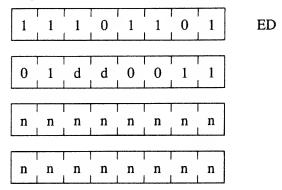

ADD A, (IX + d)

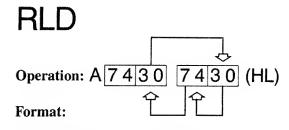

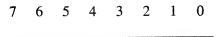

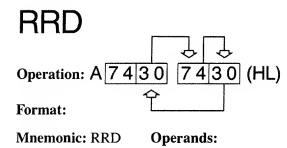

RRD

TERMS AND CONDITIONS OF SALE AND LICENSE OF RADIO SHACK COMPUTER EQUIPMENT AND SOFTWARE PURCHASED FROM A RADIO SHACK COMPANY-OWNED COMPUTER CENTER, RETAIL STORE OR FROM A RADIO SHACK FRANCHISEE OR DEALER AT ITS AUTHORIZED LOCATION

#### LIMITED WARRANTY

#### I. CUSTOMER OBLIGATIONS

A. CUSTOMER assumes full responsibility that this Radio Shack computer hardware purchased (the "Equipment"), and any copies of Radio Shack software included with the Equipment or licensed separately (the "Software") meets the specifications, capacity, capabilities, versatility, and other requirements of CUSTOMER

B CUSTOMER assumes full responsibility for the condition and effectiveness of the operating environment in which the Equipment and Software are to function, and for its installation

#### II. RADIO SHACK LIMITED WARRANTIES AND CONDITIONS OF SALE

A For a period of ninety (90) calendar days from the date of the Radio Shack sales document received upon purchase of the Equipment. RADIO SHACK warrants to the original CUSTOMER that the Equipment and the medium upon which the Software is stored is free from manufacturing defects. THIS WARRANTY IS ONLY APPLICABLE TO PURCHASES OF RADIO SHACK EQUIPMENT BY THE ORIGINAL CUSTOMER FROM RADIO SHACK COMPANY-QWNED COMPUTER CENTERS, RETAIL STDRES AND FROM RADIO SHACK FRANCHISEES AND DEALERS AT ITS AUTHORIZED LOCATION. The warranty is void if the Equipment's case or cabinet has been opened, or if the Equipment or Software has been subjected to improper or abnormal use. If a manufacturing defect is discovered during the stated warranty period, the defective Equipment must be returned to a Radio Shack Computer Center, a Radio Shack retail store, participating Radio Shack franchisee or Radio Shack dealer for repair, along with a copy of the sales document or lease agreement. The original CUSTOMER'S sole and exclusive remedy in the event of a defect is limited to the correction of the defect by repair, replacement, or refund of the purchase price, at RADIO SHACK'S election and sole expense. RADIO SHACK has no obligation to replace or repair expendable items.

RADIO SHACK has no obligation to replace of repair experituative terms.

RADIO SHACK makes no warranty as to the design, capability, capacity, or suitability for use of the Software, except as provided in this paragraph. Software is licensed on an "AS IS" basis, without warranty. The original CUSTOMER'S exclusive remedy, in the event of a Software manufacturing defect, is its repair or replacement within thirty (30) calendar days of the date of the Radio Shack sales document received upon license of the Software. The defective Software shall be returned to a Radio Shack Computer Center, a Radio Shack retail store.

participating Radio Shack franchisee or Radio Shack dealer along with the sales document

C. Except as provided herein no employee, agent, franchisee, dealer or other person is authorized to give any warranties of any nature on behalf of RADIO SHACK.

D. Except as provided herein, RAOIO SHACK MAKES ND WARRANTIES, INCLUDING WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

E. Some states do not allow limitations on how long an implied warranty lasts, so the above limitation(s) may not apply to CUSTOMER.

#### III. LIMITATION OF LIABILITY

A. EXCEPT AS PROVIDEO HEREIN, RADIO SHACK SHALL HAVE NO LIABILITY OR RESPONSIBILITY TO CUSTOMER OR ANY OTHER PERSON OR ENTITY WITH RESPECT TO ANY LIABILITY. LOSS OR DAMAGE CAUSED OR ALLEGED TO BE CAUSED DIRECTLY OR INDIRECTLY BY "EQUIPMENT" OR "SOFTWARE" SOLD, LEASED, LICENSED OR FURNISHED BY RADIO SHACK, INCLUDING, BUT NOT LIMITED TO, ANY INTERRUPTION OF SERVICE, LOSS OF BUSINESS DE ANTICIPATORY PROFITS OR CONSEQUENTIAL DAMAGES RESULTING FROM THE USE OR OPERATION OF THE "EQUIPMENT" OR "SOFTWARE" IN NO EVENT SHALL RADIO SHACK BE LIABLE FOR LOSS OF PROFITS, OR ANY INDIRECT, SPECIAL, OR CONSEQUENTIAL DAMAGES ARISING OUT OF ANY BREACH OF THIS WARRANTY OR IN ANY MANNER ARISING OUT OF OR CONNECTED WITH THE SALE, LEASE, LICENSE, USE OR ANTICIPATED USE OF THE "EQUIPMENT" OR "SOFTWARE"

NOTWITHSTANDING THE ABDVE LIMITATIONS AND WARRANTIES, RADIO SHACK'S LIABILITY HEREUNDER FOR DAMAGES INCURRED BY CUSTOMER OR OTHERS SHALL NOT EXCEED THE AMOUNT PAID BY CUSTOMER FOR THE PARTICULAR "EQUIPMENT" DR "SOFTWARE" INVOLVEO

B. RADIO SHACK shall not be liable for any damages caused by delay in delivering or furnishing Equipment and or Software.

C. No action arising out of any claimed breach of this Warranty or transactions under this Warranty may be brought more than two (2) years after the cause of action has accrued or more than four (4) years after the date of the Radio Shack sales document for the Equipment or Software, whichever first occurs

D. Some states do not allow the limitation or exclusion of incidental or consequential damages, so the above limitation(s) or exclusion(s) may not apply to CUSTOMER.

#### IV. RADIO SHACK SOFTWARE LICENSE

RADIO SHACK grants to CUSTOMER a non-exclusive, paid-up license to use the RADIO SHACK Software on one computer, subject to the following provisions:

A. Except as otherwise provided in this Software License, applicable copyright laws shall apply to the Software

- B. Title to the medium on which the Software is recorded (cassette and or diskette) or stored (ROM) is transferred to CUSTOMER, but not title to the Software.

- C. CUSTOMER may use Software on one host computer and access that Software through one or more terminals if the Software permits this function.

- D. CUSTOMER shall not use, make, manufacture, or reproduce copies of Software except for use on one computer and as is specifically provided in this Software License. Customer is expressly prohibited from disassembling the Software.

E. CUSTOMER is permitted to make additional copies of the Software only for backup or archival purposes or if additional copies are required in

- E. CUSTOMER is permitted to make additional copies of the Software only for backup or archival purposes or if additional copies are required in the operation of one computer with the Software, but only to the extent the Software allows a backup copy to be made. However, for TRSDOS Software, CUSTOMER is permitted to make a limited number of additional copies for CUSTOMER'S own use.

- F. CUSTOMER may resell or distribute unmodified copies of the Software provided CUSTOMER has purchased one copy of the Software for each one sold or distributed. The provisions of this Software License shall also be applicable to third parties receiving copies of the Software from CUSTOMER.

- G. All copyright notices shall be retained on all copies of the Software

#### V. APPLICABILITY OF WARRANTY

- A The terms and conditions of this Warranty are applicable as between RADIO SHACK and CUSTOMER to either a sale of the Equipment and or Software License to CUSTOMER or to a transaction whereby RADID SHACK sells or conveys such Equipment to a third party for lease to CUSTOMER.

- B. The limitations of liability and Warranty provisions herein shall inure to the benefit of RADID SHACK, the author, owner and or licensor of the Software and any manufacturer of the Equipment sold by RADIO SHACK

#### VI. STATE LAW RIGHTS

The warranties granted herein give the original CUSTOMER specific legal rights, and the original CUSTOMER may have other rights which vary from state to state.

875-9186

# ALDS Assembly Language Development System

TRSDOS® Version 6 Operating System: Copyright 1983 Logical Systems. All Rights Reserved. Licensed to Tandy Corporation.

ALEDIT Software: Copyright 1982, 1983 Tandy Corporation. All Rights Reserved. ALASM Software: Copyright 1982, 1983 Tandy Corporation. All Rights Reserved. ALBUG Software: Copyright 1982, 1983 Tandy Corporation. All Rights Reserved. ALLINK Software: Copyright 1982, 1983 Tandy Corporation. All Rights Reserved. ALTRAN Software: Copyright 1982, 1983 Tandy Corporation. All Rights Reserved.

TRS-80® Assembly Language Development System Manual: Copyright 1982, 1983 Tandy Corporation. All Rights Reserved.

Reproduction or use without express written permission from Tandy Corporation of any portion of this manual is prohibited. While reasonable efforts have been taken in the preparation of this manual to assure its accuracy, Tandy Corporation assumes no liability resulting from any errors or omissions in this manual, or from the use of the information obtained herein.

TRSDOS is a registered trademark of Tandy Corporation.

10 9 8 7 6 5 4 3 2 1

# To Our Customers,

This Assembly Language Development System (ALDS) is a powerful tool for developing Z80 programs for the TRS-80 Models III and 4.

It contains these five systems:

ALEDIT, a Text Editor, for writing and editing source programs.

**ALASM**, an Assembler for converting source programs to Z80 object code. The Assembler contains more than:

- 50 powerful directives. Among many features, they allow you to build relocatable program sections, macro sections, index sections; generate a length byte for text storage; and control the assembly listing format.

- 30 arithmetic, logical and relational operators.

- 10 "extended" Z80 mnemonics, which expand into an entire group of Z80 mnemonics.

ALLINK, a Linker, for linking relocatable program sections into absolute object files

**ALBUG**, a Debugger, for debugging a program in memory or altering a file on disk. ALBUG is comprised of six program files: ALBUG, ALBUG/SYS, ALBUG/OVL, ALBUGX, ALBUGRES/REL and ALBUG/RES.

**ALTRAN**, a File Transfer System, for transferring a file between the Models I, II, III, 4, 12 and 16.

Note: Models I, II, 12 and 16 require the Model II ALDS package.

#### **About This Manual**

This manual assumes you already know Z80 assembly language programming and have used an editor/assembler. It contains three sections:

**Section I, Using ALDS,** begins with a sample session which shows how to create a modular program for the Models III and 4 using all five systems. Following this session are reference chapters on each system.

Section II, ALDS Assembly Language, references the source language acceptable to the ALDS Assembler. *Chapter 7* outlines the syntax for writing source lines. The remaining chapters reference all the directives, Z80 mnemonics, and extended Z80 mnemonics available.

**Section III, Error Messages,** lists the error messages that may be generated by the ALDS programs.

If you are new to Z80 assembly language programming, we suggest you read:

More TRS-80 Assembly Language Programming by William Barden, Jr. (Radio Shack Catalog Number 62-2075)

**Note:** Before going any further, please make a backup of your ALDS diskette. See your system's owners manual for instructions on making backups.

# **Notation Key**

The manual uses these notational conventions:

Dot Matrix to represent what you will see on the screen or should type.

**(KEY)** to represent a specific key you should press.

italics to represent a value you should specify.

H to represent a hexadecimal number. (For example, 4233H

represents the hexadecimal number 4233.)

\$ to represent the current value of the Assembler's location counter.

(This is actually a convention of the Assembler.)

filespec to represent a valid TRSDOS file specification. (See your

TRSDOS manual for a definition of filespec.)

# Section I/ Using ALDS

1

|     |  | Ð |

|-----|--|---|

|     |  |   |

|     |  |   |

| 240 |  |   |

|     |  |   |

|     |  |   |

|     |  |   |

# USAGE

# **Contents**

| Section I/ Using ALDS                                                                                                                                                                                                                                                                                                         |                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Chapter 1/ Sample Session Chapter 2/ The ALDS Editor Chapter 3/ The ALDS Assembler Chapter 4/ The ALDS Debugger Chapter 5/ The ALDS Linker Chapter 6/ The ALDS File Transfer System                                                                                                                                           | 11<br>23<br>29<br>43                               |

| Section II/ ALDS Assembly Language                                                                                                                                                                                                                                                                                            |                                                    |

| Chapter 7/ Assembly Language Syntax Chapter 8/ Directives Chapter 9/ Z80 Mnemonics Chapter 10/ Extended Z80 Mnemonics                                                                                                                                                                                                         | 69<br>115                                          |

| Section III/ Error Messages                                                                                                                                                                                                                                                                                                   |                                                    |

| Error Messages                                                                                                                                                                                                                                                                                                                | 325                                                |

| Appendices                                                                                                                                                                                                                                                                                                                    |                                                    |

| Appendix A/ Undocumented Z80 Instructions  Appendix B/ ALDS Object Code Format.  Appendix C/ Numeric List of Z80 Instruction Set  Appendix D/ Alphabetic List of Z80 Instruction Set  Appendix E/ Z80 Hardware                                                                                                                | 338<br>341<br>347                                  |

| Tables                                                                                                                                                                                                                                                                                                                        |                                                    |

| Table 1/ ALEDIT Command Mode Keys Table 2/ ALEDIT Editor Commands Table 3/ ALEDIT Insert Control functions Table 4/ ALEDIT Insert Mode Special Keys Table 5/ ALEDIT Line Edit Mode Subcommands Table 6/ ALEDIT Line Edit Mode Special Keys Table 7/ ALASM Switches Table 8/ Debugger Commands Table 9/ Baud Rate Change Table | 13<br>14<br>20<br>21<br>21<br>22<br>24<br>34<br>48 |

| Table 10/ Operators                                                                                                                                                                                                                                                                                                           | 64<br>66                                           |

# Chapter 1/ Sample Session

This manual is not a tutorial. To learn Assembly Language, see your computer dealer for information on helpful books.

This chapter is for those of you who want to try a session using the entire ALDS package. It demonstrates how to link separate program sections for the Models III and 4.

This session is for demonstration only. To find out how and why each system works the way it does, you will need to refer to specific chapters in this manual.

Note for Model 4: If at any time during this procedure you receive the message, "File Already Open," type:

RESET filename

This command closes the open file.

# Creating a Source File

In this session, you need to create five source program files. To do this, use the ALDS Editor. In the TRSDOS Ready mode, type:

ALEDIT (ENTER)

this loads the ALDS Editor. After it displays its heading, type:

Ι

the insert command (Do not press **ENTER**). The Editor clears the screen and prints NONAME/SRC in the upper right-hand corner. You are now in the insert mode and can insert the first source program.

#### 1. Main Program

To insert the first program, named MAIN, type the following commands (press between columns; press (ENTER) at the end of each line.):

| MAIN  | PSECT  |               |        |      |      |

|-------|--------|---------------|--------|------|------|

|       | PUBLIC | BEGIN         |        |      |      |

|       | EXTERN | PRINT, TRSDOS |        |      |      |

| BEGIN | LD     | HL,MSG1       |        |      |      |

|       | CALL   | PRINT         | #Print | Line | MSG1 |

|       | LD     | HL ,MSG2      |        |      |      |

|       | CALL   | PRINT         | ;Print | Line | MSG2 |

|       | JP     | TRSDOS        |        |      |      |

|       |        |               |        |      |      |

| MSG1 | DEFT | 'YOU WILL BE ABLE TO LINK THIS'      |

|------|------|--------------------------------------|

|      | DEFB | ØDH                                  |

| MSG2 | DEFT | 'AS EITHER A MODEL III OR 4 PROGRAM' |

|      | DEFB | ØDH                                  |

|      | END  | BEGIN                                |

When you are finished press (BREAK). This puts you in the Editor command mode. If you made mistakes, you can use the Editor commands to edit the program. They are all listed in *Chapter 2*, The ALDS Editor.

After pressing (BREAK), save this source program on disk by typing this Editor command:

#### W MAIN (ENTER)

this saves the program as a source file named MAIN/SRC. (The Editor changes the top right-hand corner display to MAIN/SRC.) Clear the edit buffer by typing:

#### K (ENTER)

the kill command and answer Y (ENTER) to the prompt. The screen will then clear.

Now repeat the same procedures for inserting and saving MOD4, MODIII, PROG4, and PROGIII. (If you have a Model 4, insert all of these programs on your Model 4—even MODIII and PROGIII. Otherwise, insert all of these programs on your Model III.)

#### 2. MOD4 Program

| MOD4   | PSECT  | ;Model 4 F | rint Routines |

|--------|--------|------------|---------------|

|        | PUBLIC | PRINT, TRS | )0S           |

| @DSPLY | EQU    | 10         |               |

| @EXIT  | EQU    | 22         |               |

| PRINT  | INC    | HL         |               |

|        | SVC    | @DSPLY     | ¡Display Line |

|        | RET    |            |               |

| TRSDOS | LD     | HL +0      |               |

|        | JP     | @EXIT      | ;Exit         |

|        | FND    |            |               |

#### 3. MODIII Program

| MODIII | PSECT  | ;Model III    | Print Routines |

|--------|--------|---------------|----------------|

|        | PUBLIC | PRINT,TRSE    | )0S            |

| VDLINE | EQU    | Ø21BH         |                |

| JP2D0S | EQU    | 402DH         |                |

| PRINT  | INC    | HL            |                |

|        | CALL   | <b>VDLINE</b> | Display Line   |

|        | RET    |               |                |

| TRSDOS | JP     | JP2D0S        | ;Exit          |

|        | END    |               |                |

#### 4. PROG4 Program

| PROG4 | PSECT  | iModel 4 Link | King Program         |

|-------|--------|---------------|----------------------|

|       | EXTERN | BEGIN         |                      |

| START | JP     | BEGIN         |                      |

|       | LINK   | 'MAIN/REL'    | Links Main Program   |

|       | LINK   | 'MOD4/REL'    | Links Print Routines |

|       | END    | START         |                      |

#### 5. PROGIII Program

| PROGIII | PSECT  | Model III Li | nking Program        |

|---------|--------|--------------|----------------------|

|         | EXTERN | BEGIN        |                      |

| START   | JP     | BEGIN        |                      |

|         | LINK   | 'MAIN/REL'   | Links Main Program   |

|         | LINK   | 'MODIII/REL' | Links Print Routines |

|         | END    | START        |                      |

When you have finished inserting all five source files, exit the Editor by typing:

#### Q (ENTER)

which returns you to TRSDOS Ready.

# Assembling a File

You should now have stored five source files:

MAIN/SRC MOD4/SRC MODIII/SRC PROG4/SRC PROGIII/SRC

To see that they are all on your diskette, check the disk directory by typing DIR (ENTER).

These files contain three types of instructions:

- Z80 mnemonics (LD, CALL, INC, and RET), which the Assembler converts into Z80 object code. *Chapter 9* describes Z80 mnemonics.

- An extended mnemonic (SVC), which the Assembler converts into a group of Z80 instructions. *Chapter 10* describes extended mnemonics.

- Directives (PSECT, EXTERN, DEFT, PUBLIC, EQU, LINK and END), which are instructions to the Assembler or the Linker. *Chapter* 8 describes directives.

To assemble the source files, use the ALDS Assembler (ALASM). In the TRSDOS Ready mode, type:

ALASM MAIN/SRC MAIN/REL (ENTER)

The assembler processes the source file MAIN/SRC into an object file named MAIN/REL. If it displays any errors, edit or re-insert MAIN/SRC and reassemble it. (An explanation of the Assembler error messages is in the Error Messages Section of this manual.)

You can assemble the other source files in the same way.

**Note:** You can omit the /SRC and /REL extensions. The Assembler knows to append them:

```

ALASM MOD4 MOD4 (ENTER)

ALASM MODIII MODIII (ENTER)

ALASM PROG4 PROG4 (ENTER)

ALASM PROGIII PROGIII (ENTER)

```

When finished, the Assembler produces these object files:

MAIN/REL MOD4/REL MODIII/REL PROG4/REL PROGIII/REL

The extension REL means that the files are relocatable. That is, they do not have absolute load and execution addresses. Because of this, they cannot be loaded and executed in their present form.

The Assembler converts them into relocatable rather than absolute files because of the PSECT directives. See *Chapter 8* for more information on the directives. See *Chapter 3* for information on operating the Assembler.

# Linking a Relocatable File

Two of the relocatable files created by the Assembler are:

PROG4/REL PROGIII/REL

which consist solely of LINK directives. They are for the ALDS Linker to process. Type:

```

ALLINK PROG4/REL PROG4 $=5200 (ENTER)

```

This causes the Linker to:

- (1) process the LINK directives, LINKing MAIN/REL and MOD4/REL to PROG4/REL.

- (2) assign absolute addresses beginning with 5200H to PROG4/REL.

- (3) save the resulting absolute object code PROG4.

You can link PROGIII/REL in the same way. (Notice that you can optionally omit the /REL extension, since the Assembler will automatically append it.) Type:

```

ALLINK PROGIII PROGIII $=5200

```

Using the same processes as above, the Linker creates PROGIII, an absolute object file, composed of MAIN/REL and MODIII/REL.

Chapter 5, The Linker, discusses the Linker itself. Chapter 8, Directives, discusses the directives which control the Linker.

### **Executing a File**

The Linker created two absolute object files:

PROG4/CMD PROGIII/CMD

which are actually two versions of the same main program. PROG4/CMD runs on the Model 4; PROGIII/CMD is for the Model III. (Model III and 4 executable programs must have the /CMD extension.)

Assuming you created these files on the Model 4, if you wish to run PROG4/CMD on your Model 4, simply type (in the TRSDOS Ready mode):

PROG4 (ENTER)

### Transferring a File

You will, of course, need to transfer the program which does not correspond with your computer to the model in which it can be used, before you can execute it. For example, if PROGIII was created on the Model 4, it would need to be transferred to the Model III. If you have a Model III and 4 and an appropriate modem or cable, you can transfer the program with the ALDS File Transfer System. It will produce a Model III or 4 disk file of PROGIII/CMD or PROG4/CMD.

To transfer PROGIII/CMD to a Model III, use the following instructions:

Connect the two systems (see *Chapter 6*, The ALDS File Transfer System for instructions).

Load the ALTRAN program on both the Model III and Model 4 by typing:

ALTRAN (ENTER)

After ALTRAN displays its menu, type:

9 (ENTER)

This puts you in the 'Mini-Terminal' mode. To test the communication of your computers, on your Model 4 type:

COMMUNICATION

This word should appear on your Model III screen as well as your Model 4 screen. Next on your Model III type:

TEST

This word should also appear on your Model III screen and your Model 4 screen. If both computer screens have "COMMUNICATION TEST" written on them, then ALTRAN is communicating in both directions. Otherwise, recheck your connection procedure (see *Chapter 6*, The ALDS File Transfer System).

Press the key on both the Model III and 4 to return to the ALTRAN menu.

On the Model 4 type:

#### 1 (ENTER)

PROGIII/CMD (ENTER)

and on the Model III type:

#### 2 (ENTER)

PROGIII/CMD (ENTER)

This transfers PROGIII/CMD to the Model III diskette and names it PROGIII/CMD.

ALTRAN re-displays its menu when it has finished the transfer. Press **BREAK** or **(1)** to exit the ALTRAN program and return to TRSDOS Ready. You can then execute PROGIII on the Model III in the same way PROG4 was executed on the Model 4 above. Type:

PROGIII (ENTER)

# **Debugging a File**

You can debug any of the object files with the ALDS Debugger on the Models III and 4. On your Model III type:

```

LOAD PROGIII/CMD (ENTER)

ALBUG (ENTER)

```

You can now debug PROGIII/CMD by entering:

J

On your Model 4 type:

LOAD PROG4/CMD (ENTER) ALBUG

You can now debug PROG4/CMD by entering:

J

Answer the corresponding prompt with the following response:

#### Model III:

J [ADR][,BP1][,BP2][,BP3][,BP4] <E>? 5200,5200 (ENTER)

#### Model 4:

J [ADR][,BP1][,BP2][,BP3][,BP4] <E>? 5200,5200 (ENTER)

You can now single step through the program by pressing **E**.

For more information on ALBUG, refer to Chapter 4.

# LANGUAGE

# Chapter 2/ The ALDS Editor (ALEDIT)

The ALDS Editor allows you to enter and edit an assembly language source program. You can save this program on disk as a source file to be assembled into Z80 object code.

This section describes the use of the Editor itself. For information on how to write an assembly language source program, see Section II, "ALDS Assembly Language."

# **Loading the Editor**

This command, typed in the TRSDOS Ready mode:

ALEDIT source filespec

loads the Editor and then loads the specified *source filespec* into the Editor. The *source filespec* is optional. For example:

ALEDIT ENTER

causes the Editor to load and display a similar heading:

TRS-80 Model 4 Text Editor Version v.r.p. Copyright (c) 1982, 83 Tandy Corp.

(v.r.p. is the version, release and patch numbers.)

ALEDIT SORTER (ENTER)

causes the Editor to load, display the above heading, then load a source file named SORTER/SRC.

If the source filespec does not contain an extension, the Editor appends /SRC to it.

The Editor loads into all of the memory above TRSDOS. It reserves approximately the top 33K bytes in a Model III and the top 40K bytes in a Model 4 as an "edit buffer" for inserting your programs. However, if you have also loaded one of the High Memory TRSDOS utilities the edit buffer will be smaller.

# **Using the Editor**

The following pages define the three modes in which you can use the Editor:

- the command mode

- · the insert mode

- the line edit mode

#### The Command Mode

When you first load the Editor, it is in the command mode. While in this mode, you can use any of the special keys listed in *Table 1* or the commands listed in *Table 2*.

All commands except I and E return to the command mode after executing. To return to the command mode from I (insert mode) or E (line edit mode), press **BREAK** or **ENTER**) respectively.

When you enter an Editor command, it creates a blank "work line" and points to the line just beneath it. To redisplay the screen after an error message and delete the work line, use the N command.

#### Sample Use

For an example of using the command mode, use the I command to insert this program:

```

;THIS IS THE FIRST LINE (ENTER)

;THIS IS THE SECOND (ENTER)

;AND HERE IS ANOTHER (ENTER)

;AND ANOTHER (ENTER)

• END (ENTER)

```

Press (BREAK) to return to the command mode.

You can move the cursor and rearrange the lines of the program. For example type the following Editor command:

Т

the cursor moves to the top of the text. Type B to move it to the bottom. Press and to move it to specific lines.

Move the cursor to the third line and type:

1

The < appears to the left of the line. This specifies the beginning of a block. Move the cursor to the fourth line and type:

2

The > appears to the left of the line. This specifies the last line in the block. Move the cursor up to the second line and type:

0

which is the O command. This copies the block between the first and second line. Move the cursor to the next to last line and type:

D

delete command (executes without pressing (ENTER)). The last line is now deleted.

To save this program on disk you can use the W command. Type (it does not matter which line the cursor is positioned at):

#### W TEST ENTER

This saves this program on disk as a file named TEST/SRC. You can exit the Editor by typing:

#### Q (ENTER)

the quit command.

Q will exit the Editor without writing the text to disk. If you forgot to save the text first, type ALEDIT \* (ENTER) to re-enter the Editor. Your text will be retained.

Be sure you use the ALEDIT \* command immediately after you exit the Editor. It will not work predictably after you run a command which modifies memory. Also, be sure you type one blank space between ALEDIT and the asterisk(\*).

Table 1 / ALEDIT Command Mode Keys

| Model 4<br>Keys | Description                                                                                        | Model III<br>Keys |

|-----------------|----------------------------------------------------------------------------------------------------|-------------------|

| •               | moves the cursor one position to the left.                                                         | •                 |

| •               | positions the cursor down one line (ignored if the cursor is not in the first column)              | •                 |

| •               | positions the cursor up one line (ignored if the cursor is not in the first column)                | •                 |

| CTRL (A)        | positions the cursor to the top of the screen.                                                     | SHIFT • B         |

| CTRL B          | positions the cursor to the bottom of the screen or to the first line after the last line of text. | SHIFT • C         |

| •               | displays the current line sequence number. This number will change as you insert and delete lines. | •                 |

| #line(ENTER) | positions the cursor to the specified<br>line sequence number and moves<br>that line to the top of the screen. | #line( <u>ENTER</u> ) |

|--------------|----------------------------------------------------------------------------------------------------------------|-----------------------|

| (BREAK)      | cancels any command being executed and returns to the command mode.                                            | (BREAK)               |

| SHIFT)       | cancels the current command line if you have not yet pressed (ENTER).                                          | SHIFT) •              |

#### Table 2/ ALEDIT Editor Commands

#### **Description of Terms**

#### current line

the line where the cursor is currently positioned.

#### del

(stands for delimiter) One of the following characters which marks the beginning and ending of a string:

#### string

one to 37 ASCII characters on the Model 4 and one to 29 ASCII characters on the Model III.

#### text

the source program or text currently in RAM.

#### A (ENTER)

Re-executes the last executed command. This command only works with the Editor Commands C, F, X, L and W.

#### В

Moves the cursor to the bottom of the text.

#### C del string1 del string2 del occurrence (ENTER)

Changes *string1* to *string2* for the number of occ*urrences* you specify. Occurrences must range from 1 to 255. The changes begin at the current line and are made only to the first occurrence on a given line.

If you omit *occurrence*, only the first occurrence of string1 is changed. You may specify *occurrence* with an asterisk, in which case the change is made to the first occurrence of string1 in all the remaining lines.

#### For example:

#### C/TEXT/FILE/3 (ENTER)

changes the first 3 occurrences of TEXT to FILE.

#### C?TEXT?FILE?\* (ENTER)

changes all occurrences of TEXT to FILE. (Change acts on only the first occurrence within a line.) After executing the command, the cursor positions itself at the last change or, at the top of the file if changes went through the whole file.

#### D

Deletes the current line or block of lines. To delete a block, position the cursor at the first line in the block and type ①. Then position it at the last line and type the D command. (The block may be on several pages.) The cursor must be positioned on a line within the file.

For example:

|          | LD  | A,B |

|----------|-----|-----|

| 1        | ADD | A,1 |

|          | ADD | A,3 |

| <b>D</b> | ADD | A,4 |

|          | DEC | В   |

deletes all but the following:

LD A,B DEC B

You can cancel a block deletion after pressing ① but before typing D. To do this, press ③.

#### E

Allows you to edit the current line using line edit mode subcommands. The line will appear in reverse video (Model 4 only). See the edit mode for a listing of subcommands.

#### F del string del occurrence (ENTER)

Finds the specified occurrence of string. If you omit occurrence, finds the first occurrence of string. If you omit string, the last string specified is found. Occurrences must range from 1 to 255. For example:

#### F/TEXT/2 (ENTER)

finds the second occurrence of TEXT.

#### F/TEXT/ (ENTER)

finds the next occurrence of TEXT.

#### F ENTER

finds the next occurrence of the last specified string.

#### F% % ENTER

finds the next occurrence of five blank spaces. The Editor will search for only one occurrence of the string in each line.

#### G (ENTER)

Deletes all text from the current line to the end. You will first be prompted with:

"Are you sure?"

Type Y (ENTER) to delete; N (ENTER) to cancel.

#### H (ENTER)

Prints the entire text if entered as the first command or the specified block on the printer. To print a block, move the cursor to the first line of the block and type ①. Move the cursor to the last line of the block and type ①. For example:

|          | LD  | A,B |

|----------|-----|-----|

| <b>①</b> | ADD | A,1 |

|          | ADD | A,3 |

| H        | ADD | A,4 |

|          | DEC | В   |

prints a block of ADD instructions.

You can cancel a block printing after pressing ① but before typing H. To do this, press ③.

Press (BREAK) to terminate printing. If the printer is off-line or goes off-line during printing, some characters may be lost.

I

Enters the insert mode for inserting lines just before the current line. See "Insert Mode" for more information.

J

Displays current size of text and how much memory remains. Memory size does not include a small work area when the buffer is full, but the text size may reflect some of this work area.

#### K (ENTER)

Deletes ALL text. (Does not delete text from the disk file, only from the edit buffer. Before deleting your text, the Editor will ask you "Are you sure". Type Y (ENTER) to execute the command; N (ENTER) to not execute it.

#### L filespec \$C ENTER

Loads *filespec* into the Editor. \$C is optional. If specified, the Editor chains the new filespec to the end of the text currently in memory. If not specified, the new filespec overlays the current text.

For example:

#### L TEST (ENTER)

loads TEST/SRC into the Editor.

#### L TEST \$C (ENTER)

chains TEST/SRC to the end of the text currently in memory.

The Editor will load fixed length record (FLR) files with a record length of one. If the file is fixed length, each line must be ended with a carriage return.

Note: When the Editor completes, the record length will be 256.

#### М

Moves the specified block just ahead of the current line. Use ① and ② to specify the block. The Editor displays a line count as it moves each line. For example:

|          | ADD  | A,B  |

|----------|------|------|

| <b>①</b> | PUSH | DE   |

|          | PUSH | HL   |

|          | PUSH | ΙY   |

| 2        | PUSH | BC   |

|          | LD   | A,8  |

| (M)      | ADD  | A.10 |

moves the block of PUSH instructions just ahead of the last line:

| ADD  | A,B  |

|------|------|

| LD   | A,8  |

| PUSH | DE   |

| PUSH | HL   |

| PUSH | ΙY   |

| PUSH | BC   |

| ADD  | A,10 |

You can cancel the block after specifying it but before typing M. To do this, press ③.

#### N

Updates the display. You might want to use this after executing the J command or cancelling the G command.

#### 0

Copies the specified block just above the current line. (Use 1) and 2 to specify a block as described in the M command.)

#### P

Moves the cursor to the next page (which is 24 lines from the top of the screen on the Model 4 and 17 lines on the Model III).

#### O (FNTER)

Exits the Editor. If you forgot to save the file first, type ALEDIT \* (ENTER) immediately upon exiting the Editor. The Editor will load with your text retained in memory.

#### R (ENTER)

Deletes the current line and enters the insert mode. Using the J command, if there is 0000 memory left in the buffer, executing the R command will delete the line but will not allow it to be replaced with new text.

#### T

Moves the cursor to the top of the text.

#### U

Moves the cursor to the previous page (which is the 24 preceding lines for Model 4 and 17 lines for Model III).

#### V

Scrolls current line to the top of the screen.

#### W filespec \$option1 ... ENTER

Saves all text on disk as *filespec*. *filespec* is optional; if omitted, it is the filespec you used to load the file. The Editor appends /SRC to filespec unless it already includes an extension.

The options are:

E Exits the Editor after saving the file unless there is an

error.

L, ML, OR LM Saves the file with line numbers in this format: ASCII

line number/dummy TAB/text.

M Saves the file as a fixed length record (FLR) file with a

LRL of 256 in this format:

text/carriage return

This option is the default. You can use ALEDIT to edit a "DO-file" created with the TRSDOS "BUILD" command and save this format, which can be loaded

by the TRSDOS "DO" command.

#### For example:

#### W SAMPLE (ENTER)

saves all text as a file named SAMPLE/SRC.

#### W SAMPLE \$E

saves text as SAMPLE/SRC. The Editor will exit back to TRSDOS Ready after saving the file.

Without using the L or the M options, the Editor saves the file in the format required by the ALDS Assembler:

- Each character is saved exactly as it appears on the display.

- No carriage returns or end of text code is saved.

· Each line is saved in this format: length/text/

#### X del string1 del string2 del occurrence

Same as the C command, but prompts before making the change. Occurrence must range from 1 to 255.

#### The Insert Mode

The I command gets you into the insert mode. Type:

Ι

(Do not press **ENTER**).) The editor clears the screen and positions the cursor at the upper left-hand corner. You can now insert source lines into the edit buffer.

Do not use line numbers. The Assembler will consider them syntax errors.

Each source line may have up to 78 characters. After typing the line, press **ENTER** to insert it. To cancel it and return to the Editor command mode, press **BREAK**. For example:

```

;THIS IS THE FIRST LINE (ENTER)

;THIS IS THE SECOND (ENTER)

;AND HERE IS ANOTHER (BREAK)

```

inserts only the first two lines in the Editor's memory; then returns to the Editor command mode.

While inserting lines, you might find it convenient to use the key. This key is used as a tab key. The Editor has tabs set every eight columns.

The Editor offers certain control functions for quick insertion. To activate a control function, press the **CTRL** on the Model 4 or **SHIFT** on the Model III, at the same time you press the function key. For example, pressing these keys at the same time:

```

Model 4: CTRL®

Model III: (SHIFT) → ®

```

causes the Editor to insert a semicolon and the current date in the text and then position the cursor on the next line.

```

Model 4: CTRLE

Model III: SHIFT • E

```

causes the Editor to insert ":", tab to the next tab stop, insert "EQU", and then tab again to the next tab stop.

If the line becomes full while inserting the control function, the Editor stops and awaits the next insert mode instruction.

Table 3 lists all the insert control functions.

Table 4 lists the special control keys available in the insert mode.

**Note:** When the edit buffer is full, it will give you a buffer full message and return to the command mode.

**Table 3/ ALEDIT Insert Control Functions**

| 100007.1224         |                                                             |                       |

|---------------------|-------------------------------------------------------------|-----------------------|

| Model 4<br>FUNCTION | INSERTS                                                     | Model III<br>FUNCTION |

| (CTRL)(D)           | ;current date ENTER<br>(i.e. ;02/25/83 ENTER)               | SHIFT • D             |

| CTRLE               | : <b>①</b> EQU <b>①</b>                                     | SHIFT) • E            |

| CTRL G              | • GLOBAL •                                                  | SHIFT • G             |

| CTRL)(L)            | • INCLUDE • '                                               | SHIFT • L             |

| CTRL N              | ; • ENTRY: •                                                | SHIFT • N             |

| CTRL O              | { (open braces)                                             | SHIFT • 0             |

| CTRL)P              | PUBLIC                                                      | SHIFT P               |

| CTRL Q              | } (closed braces)                                           | SHIFT) • Q            |

| CTRL (R)            | ; ① EXIT: ①                                                 | SHIFT • R             |

| CTRL\S              | ;********** (ENTER)<br>(semicolon followed by 64 asterisks) | SHIFT • S             |

| CTRL)T              | ^                                                           | SHIFT T               |

| CTRLU               | ; ① USES: ①                                                 | SHIFT • U             |

| CTRL V              | [                                                           | SHIFT • V             |

| CTRL X              | EXTRN                                                       | SHIFT • X             |

| CTRL Y              | displays the tab positions. Nothing is inserted.            | SHIFT • Y             |

| (CTRL)(Z)           | ;———— (ENTER)<br>(semicolon followed by 64 dashes)          | SHIFT → Z             |

| CTRL SHIFT F        | ~                                                           | SHIFT • 6             |

| (CTRL) •            | ]                                                           | SHIFT •               |

Table 4/ ALEDIT Insert Mode Special Keys

| •       | moves cursor back one space and deletes a character                                                                                           |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| ENTER   | ends current line, carriage return, and goes to next line still in "I" mode. <b>Note:</b> (ENTER) inserts a blank line if executed by itself. |

| (BREAK) | cancels current line, and returns to CMD-mode with the cursor on the next line.                                                               |

| •       | moves to next tab position on the line. <b>Note:</b> • will reverse tab.                                                                      |

#### The LINE EDIT MODE

The E command enters the line edit mode for editing characters within the current line. When you enter this mode, the Editor displays the line in reverse video on the Model 4 only. You can then use any of the edit subcommands listed in *Table 5* or the special edit keys listed in *Table 6*.

For example, assume the cursor is on the following line:

THIS IS THE FIRST LINE

To change the word FIRST to THIRD from the command mode, type:

Ε

(Do not press **ENTER**).) The Editor will display the line in reverse video (Model 4 only). You are now in the line edit mode.

Use the **SPACEBAR** to position the cursor at the F in FIRST and type:

5CTHIRD ENTER

This stores the change and returns to the Editor command mode.

Table 5/ ALEDIT Line Edit Mode Subcommands

| COMMAND  | DESCRIPTION                                                                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| A        | Clears all changes and re-enters the edit mode for the current line.                                                                                    |

| nCstring | Changes the next n characters to the specified <i>string</i> . If n is omitted, only one character is changed. (Press SHIFT) to exit the change early.) |

| nD       | Deletes <i>n</i> characters. If <i>n</i> is omitted, one character is deleted.                                                                          |

| E        | Exits the edit mode and stores changes.                                                                                                                 |

| Hstring  | Deletes the remaining characters, enters the insert mode and allows you to insert a <i>string</i> .                                                     |

| lstring     | Allows you to insert material beginning at the current cursor position on the line. Pressing (4) will delete characters from the line. The line may be up to 78 characters in length on the Model 4 and 61 characters in length on the Model III. |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nKcharacter | Kills all characters preceding the <i>n</i> th occurrence of the <i>character</i> .* If n is omitted, the first occurence is used. If no match is found, the rest of the line is killed.                                                          |

| L           | Moves cursor to beginning of line.                                                                                                                                                                                                                |

| Q           | Quits the edit mode, cancelling all changes.                                                                                                                                                                                                      |

| nScharacter | Positions the cursor at the nth occurrence of character.* If no match is found, positions the cursor at the end of the line.                                                                                                                      |

| Xstring     | Moves the cursor to the end of the line, enters the insert mode, and allows you to insert a <i>string</i> .                                                                                                                                       |

<sup>\*</sup>The compare begins on the character following the current cursor position.

#### Table 6/ ALEDIT Line Edlt Mode Special Keys

| (SPACEBAR) | Moves cursor one position to the right.                                                             |

|------------|-----------------------------------------------------------------------------------------------------|

| SHIFT)     | Returns to edit command mode from the I, X, C, or H subcommands.                                    |

| <b>①</b>   | Moves cursor to next tab position (or the end of the line) while in the I, X, or H subcommand mode. |

| •          | Moves cursor one position to the left.                                                              |

| (ENTER)    | Identical to the E subcommand.                                                                      |

# Chapter 3/ The ALDS Assembler (ALASM)

The ALDS Assembler produces Z80 object code. It does this by inputting a source file—composed of Z80 instructions, assembler language directives, and data—and assembling it into Z80 code.

In this Section, we'll show how to use the Assembler. For information on the source file, see the sections on the ALDS Editor, Assembler Language Directives, and Z80 Instruction Set.

# The Assembler Command

This command, typed in the TRSDOS Ready mode, loads and executes the Assembler:

ALASM filespec1 filespec2 {switches}

*filespec1* is the source file you want assembled. If you do not specify an extension, the Assembler assigns it the extension /SRC. *filespec1* must not be read protected. Do not specify a password.

filespec2 is optional. It stores the assembled object code. You can specify filespec2 with an asterisk (\*). If so, the Assembler assigns it filespec1's name (less the extension).

If the program is relocatable and filespec2 does not have an extension, the Assembler assigns it the extension /REL. (The Assembler uses the PSECT directive, discussed in *Chapter* 8, to determine whether the program is absolute or relocatable.)

filespec2 overrides any OBJ directive you have in your program. filespec1 and filespec2 must be in the standard TRSDOS filespec notation.

#### **Examples:**

ALASM TEST TEST (ENTER)

assembles TEST/SRC and saves the object code as TEST if the program is absolute or TEST/REL if it's relocatable.

ALASM TEST \* (ENTER)

does the same.

ALASM TEST/PAY \* (ENTER)

assembles TEST/PAY and saves the object code as TEST or TEST/REL.

ALASM TEST/PAY FILE/ACC (ENTER)

assembles TEST/PAY and saves the object code as FILE/ACC.

ALASM TEST (ENTER)

assembles TEST/SRC. No object file is produced unless TEST/SRC contains an OBJ directive.

# **Switches**

You may specify one or more switches to create a listing or control the assembly output. If you do not specify filespec2, you must enclose the switches in parenthesis. For example:

ALASM TEST \* L (ENTER)

assembles TEST/SRC into TEST or TEST/REL and displays a listing (L) of the assembly.

ALASM TEST \* LXP (ENTER)

does the same as the above and also creates a cross reference listing (X) and prints it all on the printer (P).

ALASM TEST (L) ENTER

assembles TEST/SRC and creates a listing. Since filespec2 is omitted, the parenthesis are required.

The details of all the available switches are in Table 7:

#### Table 7/ ALASM Switches

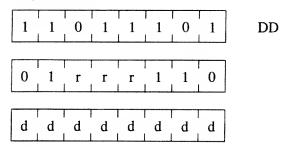

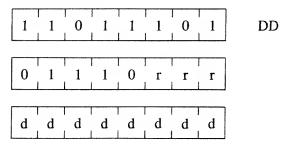

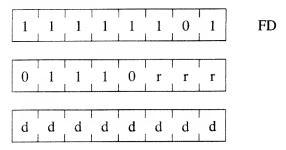

#### L (Listing)

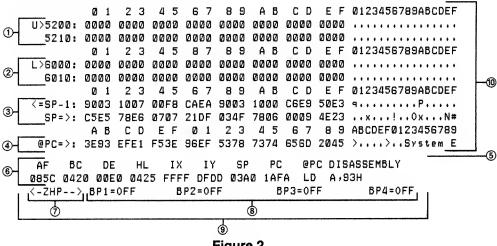

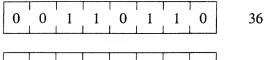

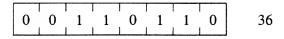

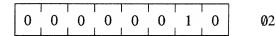

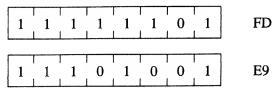

Generates a complete listing on the video display *Figure 1* shows a sample assembly listing on the Model 4.

The Assembler prints a character to the left of a line number if the line is affected by one of these special conditions:

| Character | Condition                                                |

|-----------|----------------------------------------------------------|

| -         | the symbol in symbol field is never referenced           |

| р         | the symbol in symbol field is PUBLIC                     |

| g<br>g    | the symbol in symbol field is GLOBAL                     |

| +         | a symbol in operand field is defined in global file      |

| x         | a symbol in operand field is defined in an external file |

| r         | some or all the object data is relocatable               |

#### X (Cross Reference)

Generates an alphabetical cross reference listing of all symbols defined in the program.

#### P (Printer)

Outputs the listing on the printer in addition to the video display. Use this option with the L option. You may not use this switch with the Assembler D switch, nor can you use it with the TRSDOS SPOOL command's "capture file" option (the "N" option). Be sure that the printer is on-line.

#### W (Wait On Errors)

Causes the Assembler to stop the listing at each assembly error. Press (ENTER) to continue the listing.

#### T (Truncate the Listing)

Truncates the listing output to the printer so that you can use 80 column paper.

#### **Ddrive number (Store Listing on Disk)**

Stores the listing in a disk file named *filespec1/LST*. Use this option with the L option. If the listing will not fit on the diskette, the Assembler closes the file and prompts you to change diskettes. Do so and press (ENTER). (Be sure the diskette you remove does not contain the source, object, ALASM files or important data.)

The Assembler stores the remainder as *filespec1*/LSU on the newly inserted diskette. If this diskette also becomes full, the listing goes to the next diskette as *filespec1*/LSV.

The Assembler repeats this process until it has saved the entire listing. Each time it creates a new listing file, it will increment the third character in the extension:

filespec1/LST, filespec1/LSU, ... filespec1/LSZ, filespec1/LSA, filespec1/LSB, ... filespec1/LSS

You may optionally omit the drive number. If you do so, the Assembler outputs the listing file to the lowest numbered write-enabled drive (usually drive 0) and continues the listing in the next drive. This is not a good method to use, since the Assembler might run out of work space before completing the listing.

Files created with the D option should be printed with the LIST command.

The D switch overrides the P switch.

#### G (Go)

Executes the program after assembling it. The program must be absolute and have no errors.

#### F (Memory image)

Causes the assembled object file to be in memory image form, rather than the TRSDOS program file format. The program must be absolute and have no errors. See the NOLOAD directive in *Chapter 8* for more information.

#### Examples:

#### ALASM SOURCE OBJTST LDX (ENTER)

assembles SOURCE/SRC into OBJTST/REL or OBJTST. Displays a listing and a cross reference of this assembly and saves these in one or more files named SOURCE/LST, SOURCE/LSU, SOURCE/LSV, etc.

#### ALASM TEST \* G (ENTER)

assembles TEST/SRC into TEST or TEST/REL, then executes the program (unless it is relocatable or has errors).

#### ALASM MOD1 PROG/CMD LPW (ENTER)

assembles MOD1/SRC into PROG/CMD and generates a listing which is printed on the video display and the printer. Each time the Assembler encounters an error, it stops the listing.

#### ALASM XYZ/COD TST/ABC:2 LD3 (ENTER)

assembles XYZ/COD and stores it as TST/ABC on the diskette in drive 2. The Assembler generates a listing which it displays and saves as XYZ/LST on the diskette in drive 3. If the drive 3 diskette becomes full, the assembler prompts you to insert another diskette to hold XYZ/LSU, a continuation of the listing.

**Note:** Be sure the CLOCK is not turned on (CLOCK (OFF)) while running the Assembler.

```

Tandy Corp. ALDS ALASM copr. 1982,83 v.03.02

07/01/83

Source=TEST/SRC

Object=TEST

Pass No. 1 Complete

0000'

00001

THIS IS THE FIRST LINE

0000'

; AND HERE IS ANOTHER

00002

0000'

00003

; AND ANOTHER

0000′

00004

;THIS IS THE SECOND

0000′

00005

; AND HERE IS ANOTHER

0000'

00006

END

No Assembly Errors

Time = 0:01

Bytes=0

Lines=6

Pass No. 2 Complete

```

Figure 1

|  |  |   | , |  |

|--|--|---|---|--|

|  |  |   |   |  |

|  |  |   |   |  |

|  |  | , |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

# Chapter 4/ The ALDS Debugger

The ALDS Debugger is an easy-to-use system for debugging absolute object code programs. It includes all the features found on the DEBUG utility program of your TRSDOS disk. In addition, it includes several new, powerful debugging tools.

The Model III and Model 4 Debugger are on your system diskette in the module ALBUG/CMD.

**Note:** This module resides in all memory above E000H (57344 decimal), therefore it cannot be used by programs which exceed this amount. This also means ALBUG should not be used on the Model III within a DO file, or on the Model 4 when certain high memory drivers are loaded.

Among many other features, the ALDS Debugger allows you to:

- set both permanent breakpoints with pass counts and temporary breakpoints (see the J and B commands in *Table 8*).

- execute one or more instructions at a time (see the I and E commands in *Table 8*).

- specify a memory address as an offset. This is useful in debugging a program which you assemble in the relocatable mode (see the O command in *Table 8*).

What you can debug with the ALDS Debugger:

You can debug any absolute program. The program must lie in memory between 5200H and DFFFH on the Model III and between 3000H and DFFFH on the Model 4.

In addition, you can use the Debugger to change the contents of disk files, using the DISK ZAP mode (see the Z command).

# **Loading The ALDS Debugger**

To use the Model III or Model 4 Debugger you must first load the program that you wish to debug with the TRSDOS LOAD command. Refer to your TRSDOS III or 4 Disk System Owner's Manual for more information. For example type:

LOAD filespec (ENTER)

Next you must turn on the ALDS Debugger by typing:

ALBUG (ENTER)

The Debugger display appears on your screen and you are now in the Debugger command mode. You can use any of the commands listed in *Table 8*. In order to begin debugging or executing your program, you must change the PC register to the address of the beginning of your program by using the "R" command.

If you wish to enter the Debugger without loading one of your programs (i.e. to enter the DISK ZAP mode), from the TRSDOS Ready mode type:

ALBUG (ENTER)

The Debugger begins execution.

#### The Debugger Display

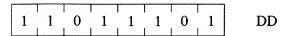

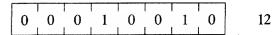

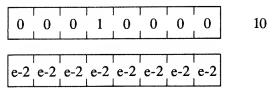

This is a sample Debugger display.

Figure 2

Refer to Figure 2 for reference to the following explanations:

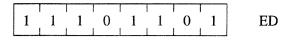

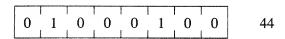

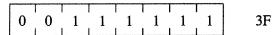

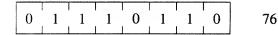

- 1. Upper Dump. This is a 32 byte section in the memory. U stands for Upper Dump. The 5200 signifies that the memory address of the first byte in that row is 5200H. When you load ALBUG this address is automatically set to 3000H on the Model 4 and 5200H on the Model III. To the right of the 5200 are the contents of memory locations 5200H through 520FH. To the right of the 5210 are the contents of memory locations 5210H through 521FH. Above these lines are numbers which represent the memory address of the data listed below them. For example, the byte under the 7 and in the row marked as 5200, is the memory location 5207H.

- 2. Lower Dump. This is another 32 byte section of memory. It is arranged exactly like the Upper Dump, except that it is originally set to 6000H on the Model III and 3000H on the Model 4.

- 3. The memory location pointed to by one of the register pairs (in this case SP) is displayed here along with the 15 bytes immediately following it. The label of this line is SP = >. Directly above it is a line labeled <SP-1. It contains the 16 bytes preceding the memory location pointed to by the register pair.

(The byte on the far left of the line is at the address (SP)-16 and the byte on the far right is at the address (SP)-1.)

- 4. The memory location pointed to by the PC is on this line, marked @PC = >. It is followed by the contents of the next 15 bytes in memory. Above this line is the memory location of the respective bytes.

- This line (here shown blank) displays certain information such as base register addresses and math function results. When you enter a new command, it is erased.

- 6. These lines show the contents of the Z80 registers. At the right side of the lower line, below "@PC DISASSEMBLY", is a Z80 instruction. The address pointed to by the PC contains this instruction in machine code, and the Debugger has disassembled it into an assembly level instruction. The Debugger uses as many bytes following the PC address as necessary to make a complete instruction. This means that what is disassembled can be one to four bytes long.

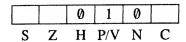

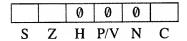

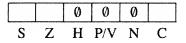

- 7. <SZHPNC> are the condition codes set in the F register. The codes are:

| S | sign          |

|---|---------------|

| Z | zero          |

| H | half carry    |

| P | parity        |

| N | BCD condition |

| C | carry         |

When a condition bit is set (i.e. when it is equal to 1) the Debugger encloses the letter within the < > characters. Otherwise it simply displays a hyphen (-). For example, <-Z---C> shows that the zero (Z) and the carry (C) bits have been set and all other bits have not.

- 8. This area lists the status of the permanent breakpoints. BP1 = 5200/000C translates as breakpoint 1 set at 5200H with the pass counter set at 12 decimal passes. BP2 = OFF means that breakpoint 2 is not set. (See *Table 8* for more information).

- 9. When you first enter the Debugger, this line gives version and copyright information. Thereafter, it displays commands and prompts used in debugging code.

- 10. This area displays the ASCII value of any hexadecimal data to its left. If the hex number has no printable value, a period (.) is displayed.

# **Entering Commands**

Table 8 lists all the Debugger commands. You can execute most of them by simply pressing the appropriate letter. By pressing (BREAK), you can abort any command in the middle of execution and return to the command level.

Most commands prompt you to specify a register or data (the prompt is in area 9 of *Figure 2*). The prompts use these abbreviations:

| Adr     | Address       |

|---------|---------------|

| Asc     | ASCII         |

| BP1     | Breakpoint 1  |

| CHR     | Character     |

| C(lr)   | Clear         |

| DEC     | Decimal       |

| <e></e> | (ENTER)       |

| Eadr    | End address   |

| H(ex)   | Hexadecimal   |

| Pas     | Pass counter  |

| Reg     | Register      |

| SAdr    | Start address |

| Str     | String        |

|         |               |

The commands usually prompt you for a certain number of parameters. If you fail to provide enough parameters, or if you use an invalid number as a parameter (e.g. hex when a decimal number is expected), you receive the message:

Illegal Parameter

and the Debugger returns to the command mode.

#### **Specifying Registers**

Certain commands require you to input a register or register pair. For example, the Debugger might prompt you with:

```

C_{+}E_{+}L_{+}A(F)_{+}B(C)_{+}D(E)_{+}H(L)_{+}(I)X_{+}(I)Y_{+}S(P) or P(C)

```

To enter a single register, you simply press the appropriate letter. To enter a register pair, you must press the letter NOT shown in parenthesis. For example, © enters the C register, but ® enters the BC register pair.

# **Specifying Data**

#### As a Constant

Some commands require constants. When entering a hexadecimal constant, you must follow it with H. For example, "10" indicates the decimal number 10, while "10H" stands for the hexadecimal number 10 (the decimal number 16).

#### As an Address

Other commands require addresses. These must be in hexadecimal. There is no need to follow hex addresses with an H.

You can specify an address by referring to a register pair which contains that address. For example, if BC contains the number 6000H, you can enter \$B

instead of the address 6000H. The register abbreviations for this type of addressing are:

| AF | \$A         |

|----|-------------|

| ВС | \$B         |

| DE | \$D         |

| HL | \$H         |

| IX | \$X         |

| IY | \$Y         |

| SP | <b>\$</b> S |

| PC | \$P         |

You can also specify any address as an "offset" to a base register. This is useful if you assemble the program in the relocatable mode. It allows you to use a relocatable location to specify an address. (See the O command in *Table 8*).

The ALDS Debugger is for debugging your own code. Hence, you cannot enter an address which is in the system memory (i.e., below 3000H on the Model 4 or 5200H on the Model III). In addition, the Debugger protects itself by not allowing you to interfere with the memory above E000H on the Models III and 4. If you enter an invalid address the Debugger returns to the command mode.

#### **Breakpoints**

The Debugger allows you to set "breakpoints" within your code. Breakpoints are commands causing the execution of your program to stop at a given point. There are two types of breakpoints, temporary and permanent.

You can assign temporary breakpoints with the J command (Jump to an address and execute). They apply only to this one execution of J. With them you can execute a short section of code, or determine which way control goes at a branch statement. (See the J command in *Table 7*).

With the B (Breakpoint) command, you can set permanent breakpoints. They remain in your program until you leave the Debugger or clear them. Permanent breakpoints may have a pass count associated with them.

You must be cautious when setting breakpoints. Set them only at the first byte of an instruction. If you are writing a self-modifying code where the first byte of an instruction may change during the course of running the program, be careful not to place a breakpoint at that instruction.

Another point of caution: If you return to TRSDOS Ready other than through the Q(quit) command, the breakpoints will not automatically clear. If you return to ALBUG without reloading your program, the breakpoints will still be there, although they will not be displayed in the display area. You must personally reset them by using the M(modify memory) command.

#### **Table 8/ Debugger Commands**

#### n; (semicolon)

Advances the memory location of the Upper Dump. The default advance is 16 bytes. You can precede the semicolon with n, a decimal number, which changes the default to n bytes, until you press **BREAK**, when the default returns to 16 bytes.

#### n + (plus)

Advances the memory location of the Lower Dump. The default advance is 16 bytes. You can precede the plus sign with n, a decimal number, which changes the default to n bytes.

#### n- (minus)

Decrements the memory location of the Upper Dump. The default decrement is 16 bytes. You can precede the minus sign with n, a decimal number, which changes the default to n bytes.

#### n = (equal sign)

Decrements the memory location of the Lower Dump. The default decrement is 16 bytes. You can precede the equal sign with n, a decimal number, which changes the default to n-bytes.

#### B

Sets or clears permanent breakpoints and their pass counters. After you press (B), a prompt appears:

1,2,3,4 or C(lr)?

You can now choose to set or alter any of the four breakpoints, or clear all four. To set breakpoint 1, for example, press ①. The Debugger prompts with:

$$\emptyset < E > \text{ or } [Adr][Pas] < E > ?$$

You can now select the address where you want the breakpoint. You must set it at the first byte of an instruction. You can not place a breakpoint on top of an existing breakpoint.

Each permanent breakpoint is associated with a pass counter. Pass counters are useful to stop execution after an instruction has been executed a given number of times. A pass count is specified by following the breakpoint address with a comma and then the pass count value.

To set the breakpoint at 6000H, with a pass of 12 type:

#### 6000,12(ENTER)

You can clear the breakpoint by entering a value of 0:

#### 0 (ENTER)

To clear all four of the breakpoints, press © in response to the first prompt. The Debugger asks you:

Are You Sure (Y/N)?

to allow you to change your command (the Debugger accepts only Y or N). The status of all four breakpoints is displayed in area 8 of *Figure 2*.

When you set each breakpoint, the Debugger saves the contents of the breakpoint address, and replaces it with an RST 18H instruction on the Model 4 which assembles into 0DFH or an RST 30H instruction on the Model III which assembles into 0F7H. Now, in typing Y to remove the breakpoints, the Debugger restores the memory addresses to their original contents.

The contents of the pass counter can be updated without respecifying the address of the breakpoint. For example, if you had previously set a permanent breakpoint at 5200H, you can update the pass count to 24 by typing:

,24 (ENTER)

in response to:

0 < E > or [Adr][,Pas] < E > ?

Whenever ALBUG executes a program instruction which is associated with a permanent breakpoint with a nonzero pass count, the count is decremented and execution resumes. Execution halts when a permanent breakpoint with a pass count of zero is reached. ALBUG is designed so that once execution is halted by reaching a pass count of zero, you may single step over a permanent breakpoint.

The permanent breakpoint remains in the program until it is explicitly cleared with the (1) command or until ALBUG is exited with the (1) command. Note: if a return to DOS is executed in your program, the permanent breakpoints remain intact and ALBUG can be re-entered by typing ALBUG.

ALBUG uses RST 18H instructions on the Model 4 and RST 30H instructions on the Model III to handle all breakpoint processing. If ALBUG encounters an RST 18H instruction on the Model 4 or an RST 30H instruction on the Model III, which you placed in your program, execution will halt. To resume execution, the program counter must be reset using the (R) command.

C

Copies one section of memory to another. After you press ①, a prompt appears:

Start Adr, End Adr, To Adr <E>?

Type the appropriate start, ending, and destination addresses. For example, type:

5800,582F,6000 (ENTER)

to copy the data contained in addresses 5800H-582FH to addresses 6000H-602FH.

#### D

Dumps the data contained in the address pointed to by a register pair in the Debugger display. (See area 3 in *Figure 2*). The data on either side of this address is also displayed. After you press ①, the Debugger displays:

Reg Dump B(C),D(E),H(L),(I)X,(I)Y,S(P) or P(C)?

To see the data referenced by the IX register pair, respond with:

$(\mathbf{X})$

The screen updates to display the new dump.

#### nE

This command is identical to the ① command with one exception: If the current instruction is a call the debugger executes the entire routine.

#### nF

Searches for a string within a given range in the memory. After you press **(F)**, a prompt appears:

Sadr, Eadr <E> or <E>?

After you enter a valid start and end address, the Debugger asks you:

H(ex) or A(scii)?

Depending on whether you enter H or A, the Debugger then prompts you with:

Hex Str <E>?

0

Asc Str <E>?

When you enter the appropriate type string the Debugger searches through the given memory for it. If the Debugger finds a matching string, the Lower Dump is set to display this part of memory. If no match is found, the Debugger returns to the command level.

To find the next occurence of the string, you need only to press (F) from the command level and respond to the prompt with (ENTER). You can continue to search for matching strings until you reach the ending address (EAdr) or until there are no more string matches in the specified range.

To specify which occurrence of the string you want to find, precede the F command with n, a decimal number between 1 and 254. For example, to find the fifth occurrence of 1FH, start by entering 5F.

The F command will find an ASCII string of up to 24 characters or a HEX string of up to 12 digits.

You may also specify a new range for the current string. Enter the new range, abort the **(F)** command with the **(BREAK)** key at the 'H(EX) or A(SCII)?' prompt, and press:

F (ENTER).

G

Examines a 256 byte area in memory. After you press (3), a prompt appears:

U(pper) or L(ower)?

Depending on your answer, the Debugger displays the 256 byte multiple of memory which contains the address of the Uppper or Lower Dump. For example, if the Upper Dump starts at 5207H and you press (and then (J), your screen changes so that it now contains a dump of memory starting with 5200H.

The  $\langle n; \rangle$ ,  $\langle n-\rangle$ ,  $\langle n-\rangle$ , and  $\langle n+\rangle$  commands may be used in this display mode as they were in the partial screen display mode, except that the value of n is always rounded up to a multiple of 256.

Press (BREAK) to return to the regular Debugger display.

#### nl

The ① and ② commands are ALBUG's single step instructions. The ② command executes the current instruction in your program (the instruction pointed to by the PC register.) ALBUG then increments the PC register to the next instructions address and returns to the command mode.

By preceding ① with n, a decimal number, you can indicate the number of times it is to be repeated. For example, if you type:

101

the ① command is executed 10 times.

There are a couple of considerations you should be aware of when single stepping. ALBUG will not place a breakpoint in a protected area. This implies that an attempt to single step an instruction in a protected area will cause a jump to that instruction. Single stepping a call to a protected area will cause the entire call to be executed at full speed. These precautions are necessary since many of the system calls such as video and disk I/O will work properly only when executed at full speed.

J

J[ADR][,BP1][,BP2][,BP3][,BP4] < E > ?

The start address (ADR) is optional. If you omit it, the execution begins at the contents of the PC. BP1-BP4 are temporary breakpoints and are also optional. You can include any or all of them.

The first temporary breakpoint encountered causes the execution to terminate. This clears all temporary breakpoints. The execution also terminates if a permanent breakpoint with a pass of zero is encountered.

For example, suppose you want to execute the instructions between 5200H and 5221H, inclusively. After pressing ①, you would type:

5200.5221 (ENTER)

Temporary breakpoints are often useful near branch points. If you set breakpoints at the possible jump locations, you can see which way your program goes. For example, say you have a set of conditional jumps which could go to 6040H, 6080H or 60F0H. When you enter:

5800.6040.6080.60F0 (ENTER)