# Radio Shaek TECHNICAL INFORMATION SERIES

# **TRS-80**<sup>®</sup>

MODEL II GLOSSARY

0220 TECHNICAL SUPPORT SERVICES

# · TRS-80 ® ·

TRS-80® Model II Glossary: Copyrighted®, 1984

By Tandy Corporation

All Rights Reserved

TRSDOS® Operating System: Copyrighted®, 1981

By Tandy Corporation

All Rights Reserved

Reproduction or use, without express written permission from Tandy Corporation, of any portion of this manual is prohibited. While reasonable efforts have been taken in the preparation of this manual to assure its accuracy, Tandy Corporation assumes no liability resulting from any errors or omissions in this manual, or from the use of the information contained herein.

\_\_\_\_\_ TRS-80 <sup>®</sup> \_\_\_\_\_

\*\*\*\*\*\*\*\*\*\*\*\*\*\*

#### Introduction

\*\*\*\*\*\*\*\*\*\*\*\*\*

This manual is divided into five sections:

CPU Board.....Section 1

FDC (Early) Board....Section 2

FDC (Late) Board....Section 3

VDG Board....Section 4

Each section contains a glossary on most of the mnemonics listed on the respective schematics contained in the Model II Technical Reference Manual.

Memory Board......Section 5

Most of the sections also contain Port Allocation Tables, Test Point Definitions, and Standard Jumper Configurations.

This Glossary is not intended as an indepenant tutorial, but is rather a supplementary service aid to the contents of the Model II Technical Reference Manual.

Model II Technical Bulletins referenced in several sections of the Model II Glossary are contained in the newly issued TECHNICAL BULLETINS, Volume 1.

Notes on Conventions used in the Model II Glossary

In the schematics for the Model II, it is a convention to indicate in the name of "single action" control signals the logic level which is required to initiate other activity. Thus, for example, MREQ\* and RD\* from the Z8Ø indicates that logic lows will initate the sequence of activities that will result in data from memory being placed on the data bus, while MREQ and RD would indicate initiation of activity at logic highs. In this Glossary, the word "asserted" will be used to indicate such a logic level (i.e, logic low for MREQ\*), while the word "negated" will be used to indicate the logic level which does not initiate activity, or which terminates activity (i.e., logic high for MREQ\*).

This convention is not used for "dual action" control signals, since both levels will produce a desired result. For example, a logic high DIR will cause a drive head to move inward toward Track 76, while a logic low DIR will cause the head to move outward toward Track 0.

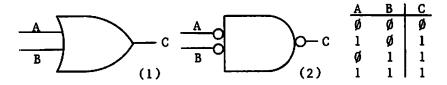

In the schematics for the Model II Boards, many logic gate symbols are shown with inversion bubbles on the input side of the gate. The logic symbols for such gates shown in the chip specification sheets, however, are not the same. For example, a function of a Quad 2-Input OR Gate, such as the 74LS32, would normally be drawn as in Diagram 1 below, but on the schematics it might be drawn as a NAND gate with two bubbles on the input side as in Diagram 2, below. Both symbols yield the same truth table shown below, and are thus functionally equivalent. Note that the negative logic equivalent to the positive logic OR gate is the AND gate: thus Diagram 2 is not the negative logic equivalent for Diagram 1.

The purpose of using a functionally equivalent-type of symbol is to emphasize the logic inputs necessary to create the logic output that will represent the asserted level of a signal from the gate. In the example of Diagram 2, a logic low represents the asserted level from the NAND gate: both inputs must be low to obtain this asserted output level.

| *** | rikri | ** | * | k x | × | *1 | t x | * | * | * | * | * | Á | À | ď | r |  | d' | * | * | * | × | × | ď | , | k: | À. | × | * | * | , | ۲í | k: | × | × | * | , |  | * | * | * | × | ď | 44 | × |

|-----|-------|----|---|-----|---|----|-----|---|---|---|---|---|---|---|---|---|--|----|---|---|---|---|---|---|---|----|----|---|---|---|---|----|----|---|---|---|---|--|---|---|---|---|---|----|---|

|-----|-------|----|---|-----|---|----|-----|---|---|---|---|---|---|---|---|---|--|----|---|---|---|---|---|---|---|----|----|---|---|---|---|----|----|---|---|---|---|--|---|---|---|---|---|----|---|

#### Section One

#### Model II CPU Board

#### \*\*\*\*\*\*\*\*\*\*\*\*\*

#### Contents

| Glossary - Sheet 3Page                | 1-3  |

|---------------------------------------|------|

| Glossary - Sheet 2Page                | 1-7  |

| Glossary - Sheet 1Page                | 1-11 |

| Test Point DefinitionsPage            | 1-15 |

| Port Allocation TablePage             | 1-17 |

| Jumper Option NotesPage               | 1-18 |

| Standard Jumper ConfigurationPage     | 1-19 |

| BISYNC Jumper ConfigurationPage       | 1-19 |

| Jumper Terminal Cross ReferencePage   | 1-20 |

| CPU Board Jumper Terminal LocatorPage | 1-21 |

The listings in this glossary are divided into 3 sections, respective to the three sheets of the CPU schematic.

When a signal from one sheet is referenced to another, a pointer, "/#", will be used to indicate the sheet: i.e. From Pin 1 of U14/2 To Pin 24 of U12/1.

The CPU schematics reflect the circuitry of the REV B Board. The latest CPU Board is REV D.

# - TRS-80 <sup>®</sup> -----

# Index for CPU Board Signals

| Signal     | Page           | Signal    | Page   |

|------------|----------------|-----------|--------|

| 8MHZ       | 1-14           | LOW 4K*   | 1-4    |

| BAI*       | 1-14           | M1*DMA    | 1-13   |

| BAKIN*     | 1-6            | MREQ*DMA  | 1-14   |

| BAO*       | 1-12           | NMIRQ*    | 1-14   |

| BUSRQ*     | 1-12           | OBWAIT*   | 1-7    |

| CECTC*     | 1-8            | OE*ROM    | 1-11   |

| CE*DMA     | 1-12           | OUT*      | 1-4    |

| CE*ROM     | 1-11           | RxCA-B    | 1-1Ø   |

| CESIO*     | 1-10           | RxDA-B    | 1-10   |

| CLK/TRGØ-2 | 1-10           | RD*DMA    | 1-14   |

| CTSA-B     | 1-10           | RDROM*    | 1-4    |

| DCDA-B     | 1-10           | RDY*DMA   | 1-13   |

| DISRO*     | 1-6            | READ*     | 1-4    |

| DMA EXT*   | 1 -5           | RESET*    | 1-8    |

| DTRA-B     | 1 <b>-</b> 1 Ø | ROMØCE*   | 1-4    |

| EIIN       | 1-6            | ROM1CE*   | 1 -4   |

| EIOUT      | 1-9            | ROM/RAM*  | 1-8    |

| FØ*-F3*    | 1-3            | ROM*/RAM  | 1-8    |

| F4*-F7*    | 1-3            | RTC       | 1-6    |

| F8*        | 1-3            | RTSA-B    | 1-1Ø   |

| F9*        | 1-3            | SELECT*   | 1-5    |

| IEOUT      | 1-6            | SHADOW*   | 1-6    |

| IN*        | 1-4            | SYNCA-B   | 1-1Ø   |

| INTAK*     | 1-5            | TxCA-B    | 1-1Ø   |

| INT*DMA    | 1-13           | TxDA-B    | 1-10   |

| INTRQL*    | 1-10           | WAIT*     | 1-7    |

| INTRQ*BUS  | 1-14           | WAIT*BUS  | 1-6    |

| I/O ADD*   | 1-3            | WR*DMA    | 1-14   |

| IORQ*      | 1-13           | Z8ØDMA 36 | 1-9    |

| KBINT      | 1-14           | 28ØDMA 38 | 1-9    |

| KBIRQ*     | 1-9            | ZC/TØ-2   | 1 -1 Ø |

#### Glossary - Sheet 3

Only the mnemonics originating from Sheet 3 of the CPU schematic will be covered under this heading.

F9\* From Pin 11 of the Port Address Decoder U36. To Pin 2 of U37, and Pin 13 of U3. When asserted, this signal indicates that the CPU is in the process of selecting or deselecting the Boot ROM. See "SHADOW\*".

F8\* From Pin 10 of the Port Address Decoder U36. To Pin 4 of U37. Also routed to Pin 1 of U3/1 as signal "CEDMA\*". When asserted, this signal indicates that the CPU is in the process of transfering control or command data to or from the DMA.

F4\*-F7\*

From Pins 5, 6, 7, and 9 of Port Address Decoder U36.

To Pin 5 of U37. Also routed to Pin 35 of U18/2 as signal "CESIO\*". This signal indicates that the CPU is in the process of writing commands or data to or from the SIO. The SIO will transmit data to the CPU when this signal is asserted during a Read cycle.

FØ\*-F3\*

From Pins 1, 2, 3, and 4 of the Port Address Decoder, U36. To Pin 1 of U37. Also routed to Pin 16 of U19/2 as signal "CECTC\*". When asserted during a Port Write, this signal indicates that the CTC is in the process of accepting control words, interrupt vectors, or time constant data words from the Bus. During a Port Read, this signal indicates that the CTC is transmitting data from one of its Down-Counters to the CPU.

I/O ADD\* From Pin 12 of U17. To Pin 1 of U16. This signal detects when any of the on-board Ports is being addressed.

IN\*

From Pin 6 of U5. When asserted, this signal indicates that the CPU is in the process of doing a Port Read. To Pin 9 of U14 where it is ORed with "OUT\*" (see same) to become signal "IN\*+OUT\*" (see same). "IN\*" is also used in the Bus Steering Logic at Pin 13 of U22.

OUT\*

From Pin 3 of U5. When asserted, this signal indicates that the CPU is in the process of doing a Port Write. To Pin 10 of U14 where it is ORed with "IN\*" (see same) to become signal "IN\*+OUT\*" (see same). Also used at Pin 12 of U3 where it is ANDed with "F9\*" to become signal "SHADOW\*" (see same).

LOW 4K\*

From Pin 11 of U5. When asserted, this signal indicates that the System Address space between 1000H and FFFFH is not being accessed. To Pin 10 of U5 where it is ANDed with signal "ROM\*/RAM" (see same) to enable the ROM gates.

READ\*

From Pin 8 of U3. This signal will be asserted during (TP 4) a Memory Read cycle. To Pin 13 of the Read ROM Gate, Ul6. Also routed to Pin 20 of Ull/1, where it is used to enable the ROM Data output lines.

RDROM\*

From Pin 11 of U16. A conditional signal to Pin 12 of the Select Gate Ul4. Asserted during a Memory Read cycle when the CPU is in the process of accessing the System Address space between 0000H and 0FFFH.

ROMØCE\*

From Pin 6 of Ul6. Chip Enable signal for the Boot (TP 3) ROM. To Pin 18 of the Boot ROM Ull. This signal will be asserted when "ROM\*/RAM" is a logic low, and when the CPU is in the process of doing a Memory Read in the Address space between 0000H and 07FFH, or the first 2K of the System Memory.

ROM1CE\*

From Pin 8 of Ul6. Chip Enable signal for a second 2K of ROM. This signal would be asserted in the Address space between Ø800H and ØFFFH. Not currently used in the Model II.

SELECT\*

(TP 15)

From Pin 11 of U14. This signal will be asserted when the CPU is in the process of doing an on-board Port Select, or ROM Read. To Pin 1 of U39/1 through which it is presented to Pin 43 of the System Bus. Signal "SELECT\*" at Pin 43 of the System Bus is not used by any external device.

Also to Pin 9 of the Bus Steering Gate U22, where it is used (TP 17) to disable the Receivers of the CPU Board Data Buffers U31 and U32 to prevent data from the System Bus from being received while the CPU is in the process of doing an on-board Port Select or ROM Read.

INTAK\*

(TP 13)

Pin 11 of U21. This signal will be asserted when the CPU is in the process of acknowledging either an on-board or an external Interrupt Request.

To Pin 3 of U13 (see note below). Also to Pin 2 of U21 where it will place Pin 10 of U22 at a logic low to disable the Receivers of the System Data Buffers when an on-board Interrupt Request is being serviced.

Note: Signal "INTAK\*" is ANDed with signal "EIOUT" if the INTRQL Mod on the CPU Board is applied for BISYNC, HD, etc: refer to Technical Bulletins II:17 and II:26 for details. This circuitry is etched onto REV D and later Boards.

When an external device is generating the Interrupt Request, Pin 10 of U22 will remain at a logic high. At this same time, Pins 9 and 11 of U22 will also be at a logic high, and the Receivers of the Data Buffers will be enabled.

DMA EXT\*

From Pin 6 of U3. To Pin 9 of U17/1 to disable the Drivers of Buffers U33, U34, and U35. Also to Pin 10 of U4 to disable the Drivers of Buffers U31 and U32. Not currently used in the Model II.

This signal would be asserted during an external device DMA operation, signified by signals "BUSRQ\*" and "BAO\*" (see same) being asserted at the same time. Were an external device DMA operation in progress, the Data, Address, and Control Drivers noted above would be disabled.

# ----- TRS-80 <sup>®</sup> -----

| SHADOW*        | From Pin 11 of U3. This signal will be asserted during a Port Write to "F9*". It is applied to Pin 11 of U13/2 as a clock to select or de-select the Boot ROM. The selection will depend on the logic status of Data bit Ø. See signal "ROM/RAM*". |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEOUT          | To Pin 14 of the Model II System Bus. From Pin 24 of U24/1, where it is labeled "EIOUT". See Glossary, Sheet 2 and Sections 2 & 3, Early/Late FDC Boards.                                                                                          |

| EIIN           | From Pin 13 of the Model II System Bus. There is no indication that this signal is used on the CPU Board.                                                                                                                                          |

| BAKIN*         | From Pin 15 of the Model II System Bus. There is no indication that this signal is used on the CPU Board.                                                                                                                                          |

| BUSRQ*         | From Pin 17 of the Model II System Bus. See Glossary, Sheet 1.                                                                                                                                                                                     |

| DISRO*         | From Pin 40 of the Model II System Bus. There is no indication that this signal is used on the CPU Board. See Section 5, Memory Board.                                                                                                             |

| KBIRQ*         | From Pin 42 of the Model II System Bus, from the VDG Board. To Pin 20 of Ul9/2. See Glossary, Sheet 2.                                                                                                                                             |

| WAIT*<br>(BUS) | From Pin 48 of the Model II System Bus. To Pin 1 of U14/2 and to Pin 12 of U4/2. See Glossary, Sheet 2.                                                                                                                                            |

| RTC            | From Pin 47 of the Model II System Bus, from the VDG Board. It is mislabeled as going to Sheet 2: there is no indication that this signal is used on the CPU Board.                                                                                |

####

#### Glossary - Sheet 2

Only the mnemonics originating from Sheet 2 of the CPU schematic will be covered under this heading.

WAIT\*

(TP 12)

From Pin 3 of Ul4. To Pin 24 of the CPU Ul2. This signal is the logical result of an on-board Wait, or a Wait generated by an external device.

The Wait from an external device enters the CPU card at Pin 48 of the Model II System Bus. For the on-board Wait, see signal "OBWAIT\*".

OBWAIT\*

From Pin 6 of Ul4. The ORed result of an on-board Wait generated during either an Op-Code Fetch cycle from RAM or during any ROM Read.

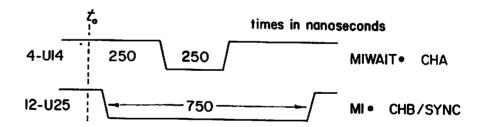

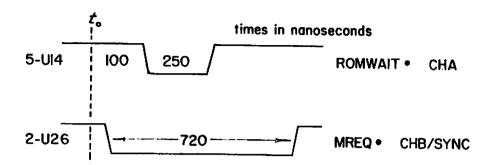

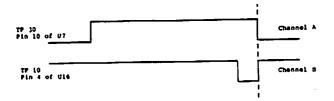

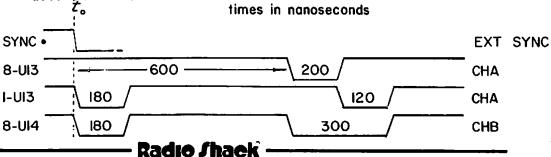

The measured timing diagrams below illustrate how a Wait is generated during an Op-Code Fetch cycle from RAM. This Wait is required to permit extension of the pre-charge period prior to memory refresh occuring in the Ml cycle. See Section 5, Memory Board.

The measured timing diagrams on the next page illustrate how the Wait is generated during a ROM Read. This Wait is required to extend the period that signal "READ\* at Pin 8 of U3/3 is asserted to permit assertion of valid data from the 300 nanosecond ROM.

ROM/RAM\*

From Pin 9 of Ul3. To Pin 5 of ROM Wait Gate U22. Also to Pin 10 of RAM Wait Gate U21.

A Power-On, or Manual Reset at Pin 10 of Ul3 will set this signal to a logic high, indicating that the Boot ROM is selected. This condition will enable the ROM Wait Gate and allow the ROM Wait Generation Logic to output a Wait with every ROM Read. See "OBWAIT\*" for the timing diagrams.

The Boot ROM will electrically switch out of the system when "SHADOW\*" (see same) is initiated with Data bit Ø set at a logic low. This condition will now block the ROM Wait Gate. The Wait Generation Logic will now output Waits with every Op-Code Fetch. See "OBWAIT\*" for the timing diagrams.

ROM\*/RAM

(TP 18)

From Pin 8 of Ul3. This signal is the inverse of signal "ROM/RAM\*" (see same).

To Pin 9 of U5/3. When the Boot ROM is selected, this signal will allow signal "LOW 4K\*" (see same) to enable the ROM gates, which are three parts of U16/3.

Switching the Boot ROM out of the System will block signal "LOW 4K\*". Thus, the first 4K of Address space can now be used to access the System RAMs.

RESET\*

(TP 11)

From Pin 4 of U29. This is the System Reset signal. It is initiated during a Power-On, or Manual Reset.

The Power-On Reset is the result of an RC timing circuit, consisting of Resistor R21 and Capacitor C38.

CECTC\*

From Pins 1-4 of U36/3. To Pin 16 of U19. The CTC Chip Enable signal from Port Address decoding.

# TRS-80 <sup>6</sup>

The Manual Reset is generated by a one-shot, flip-flop, one-shot type of circuit to limit the width of the Reset Pulse to approximately 170 microseconds. This pulse limit is necessary to avoid suspending refresh to the RAMs, should the Reset happen to occur during the T3 Clock of the Ml\* cycle of the Op-Code Fetch instruction. This possibility is prevented by synchronizing the Manual Reset circuit to signal "Ml\*" at Pin 5 of U29.

Without this synchronization, the contents of the RAMs could be destroyed should the Reset Switch be kept closed for too long a period of time.

**EIOUT**

From Pin 8 of U24. To Pin 14 of the Model II System Bus, where it is labeled "IEOUT" (see same). "IEOUT" is a loop signal of the Z80 daisy chain interrupt structure.

The order of interrupt priority on the CPU card is from the CTC U19/2, to the SIO U18/2, and to the DMA U20/1. The PIO on the FDC card is the fourth device of the chain.

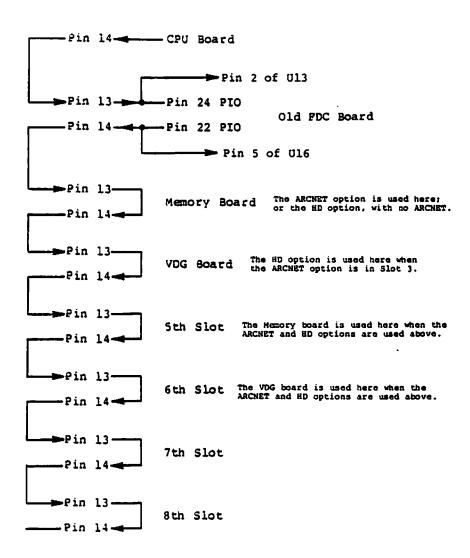

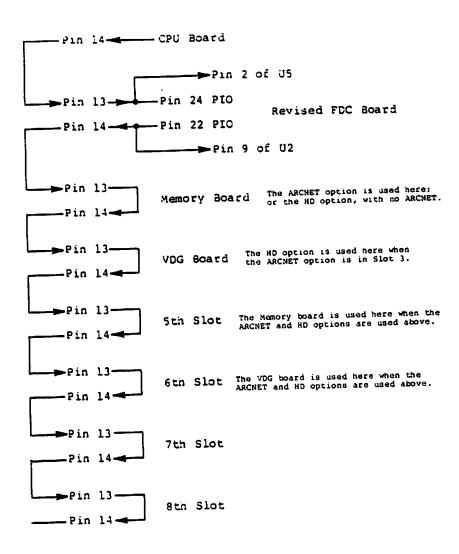

Signal "IEOUT" is routed to the PIO on the FDC card at Pin 14 of the Model II System Bus. This signal will be at a logic high when none of the devices on the CPU card is in the process of requesting an interrupt. Refer to Page 2-36 for the Mother Board loop diagram.

Z8Ø DMA Pin 38 From Pin 11 of U23. To Pin 38 of DMA U20/1 (where it mislabeled as coming from Pin 9 of U23). This is the Interrupt Enable (IEI) signal to the DMA. It is a loop signal of the Z80 daisy chain priority interrupt structure. This signal will be at a logic high when neither the CTC nor the SIO is in the process of requesting an interrupt.

Z8Ø DMA Pin 36 From Pin 36 of U20/1 (where it is mislabeled as going to Pin 11 of U24). To Pin 1 of U24. This is the DMA IEO signal used to create "EIOUT" (see same) at Pin 8 of U24.

KBIRQ\*

From Pin 42 of the Model II System Bus. To Pin 20 of U19, where it is mislabeled as "KBIRQ". Asserted as the keyboard Interrupt Request from the VDG Board.

- INTRQL\*

From Pin 12 of U19, From Pin 5 of U18, and From Pin 37 of U20/1. The on-board Interrupt Request from the CTC or SIO on Sheet 2 or from the DMA on Sheet 1. To Pin 1 of U4/1, then to the "INT\*" (see same) Pin of the CPU. Also used at Pin 4 of U13/3 to set this device, necessary so that a logic low will appear at Pin 1 of U21/3 before the CPU acknowledges the on-board Interrupt Request with signal "INTAK\*" (see same).

- CLK/TRGØ-2 From Pin 5 of U2/1. To Pins 21-23 of U19. An external 2 MHz Clock signal decrementing the CTC's three programmable Down-Counters.

- ZC/TØ-2 CTC zero count/timeout strobes resulting when the CTC Down-Counters reach zero. Used as (baud rate) clocks by the SIO at Pins 13, 14 and 27 of U18.

- CESIO\* From Pins 5-7,9 of U36/3. To Pin 35 of U18. The SIO Chip Enable signal from Port Address decoding.

- RxDA-B To Pins 12/28 of U18. RS232C (serial) data received from Pin 3 of U1Ø (A), and from Pin 11 of U8 (B).

- RxCA-B To Pins 13/27 of U18. Receiver clock (baud rate) strobes from CTC ZC/TØ and ZC/T2 outputs.

- TxCA-B To Pins 14/27 of U18. Transmit clock (baud rate) strobes from CTC ZC/Tl and ZC/T2 outputs.

- SYNCA-B From Pin 8 of U9 (A) and Pin 8 of U8 (B). To U18, Pins 11/29. External device sychronization signals.

- CTSA-B From Pin 11 of U9 (A) and Pin 3 of U9 (B). To U18, Pins 18/23. Clear-to-send enables for external logic.

- DCDA-B From Pin 3 of U8 (A) and Pin 6 of U8 (B). To U18, Pins 19/22. Data-carrier-detect from external logic.

- TxDA-B From Pins 19/26 of U18. To Pins 9/10 of U6 (A) and Pins 4/5 of U7 (B). RS232C (serial) data transmitted.

- RTSA-B From Pins 17/24 of U18. To Pins 12/13 of U6 (A) and Pins 1/2 of U7 (B). Request-to-send to external logic.

- DTRA-B From Pins 16/25 of U18. To Pins 4/10 of U7 (A) and Pins 1/2 of U6 (B). Data-terminal ready.

#### Glossary - Sheet 1

Only the mnemonics originating from Sheet 1 of the CPU schematic will be covered under this heading.

OE\*

ROM

(TP 4)

To Pin 20 of Ull. This is the product Pin description of the EPROM. An input to this Pin by signal "READ\*" (see same) is used to control the three-state Data output lines of the EPROM. The Data output lines are normally in the open, or high impedance state. The Data lines will connect to the System Bus whenever signal "READ\*" is asserted.

CE\*

(TP 3)

To Pin 18 of Ull. This is the product Pin description of the EPROM. Input to this Pin by signal "ROMØCE\*" is used to power-up the EPROM.

Note: Change Ull on the schematic to indicate that it is a ROM, and not an EPROM. These devices have the same electrical characteristics (see below).

The READ and STANDBY are the two normal modes in which the EPROM/ROM operate.

A READ operation is accomplished by placing logic low signals at the "CE\*" (see same) and "OE\*" (see same) Pins of the chip. Valid data should appear at the output approximately 300 nanoseconds after Pin "CE\*" is made low.

During the READ operation, an EPROM will dissipate approximately 525 milliwatts of power. The power dissipated by a ROM in this same mode will be slightly less.

The EPROM/ROM will switch to the STANDBY mode when Pin "CE\*" is made high. The power dissipated by either chip in this "resting" mode will about 25% of their respective READ maximums.

As a special note, Pin "OE\*" will lose its control of the Data output lines in the STANDBY mode, because now, the controlling signal has become the high on Pin "CE\*". The Data lines will remain in the tristate mode as long as signal "CE\*" is at a logic high.

# BUSRQ\* (TP 8)

From/To Pin 15 of DMA U20. This is a bi-directional signal which is tied to Pin 17 of the Model II System Bus, and to Pin 25 of the Z80 CPU.

As an output signal from DMA U2Ø, to the CPU U12, this is a request signal from the DMA for control of the System Bus. The CPU will grant this request as soon as it completes its current machine cycle by tristating its Address, Data, and Control Buses. At this same time, the CPU will also generate signal "BUSAK\*" to inform the DMA that the Buses have been released.

During multiple DMA operations, the on-board DMA would use this line as an input to sense when another DMA has sent out a request for control of the System Bus. This action would cause the on-board DMA to refrain from asking for the Bus until the other DMA has completed its operation. Not currently used in Model II.

#### BAO\*

From Pin 13 of DMA U20. This is the Bus Acknowledge Output signal for multiple DMA use. To Pin 16 of the Model II System Bus where it becomes buffered signal "BAKOUT\*". Signal "BAO\*", along with signal "BAI\*" (see same), form a daisy chain for multiple-DMA resolution over Bus control. The on-board DMA (U20) has the highest interrupt priority. Not currently used in the Model II.

#### CE\*DMA

To Pin 16 of DMA U20. This Pin has a dual purpose. It not only functions as the Chip Enable line, but is also programmed to serve as the Wait line to the DMA.

As a Chip Enable function, this line will be asserted when Port F8 (see same) is addressed and becomes signal "CEDMA\*" (see same) at Pin l of U3. Signal "BUSAK\*" (see same) will block this signal at Pin 2 of U3 when the CPU is in the process of granting a bus acknowledge.

Pin 15 of DMA U20 functions as a Wait line after the DMA has received a Bus Request Acknowledge from the CPU. This will cause wait states to be inserted in the DMA's operation cycle to slow it down to a speed that matches the Memory or I/O device. The DMA is used in Model II TRSDOS®-based software for Disk-to-Memory and Memory-to-Disk data transfers.

RDY\*

To Pin 25 of DMA U20. This is a buffered signal from Pin 41 of the Model II System Bus where it is called "XFERRQ". This signal is monitored by the DMA to determine when the FDC is ready to transfer a byte of data. To state it differently, "XFERRQ" is the transfer request signal from the FDC.

INT\*

From Pin 37 of the DMA. To Pin 1 of U4 where it becomes signal "INTRQL\*" (see same).

Ml\* DMA To Pin 26 of DMA U20. From Pin 27 of the CPU U12. This signal, along with signal "IORQ\*" (see same), is used by the DMA as an Interrupt Acknowledge.

IORQ\*

From/To Pin 10 of DMA U20. This is a bi-directional line. As an input, this signal is part of the Mode 2 interrupt scheme which the Model II supports. With Mode 2 interrupts, the CPU will form a 16-bit Memory Address where the upper 8-bits will be the contents of the CPU's "I" Register, and the lower 8-bits will come from the interrupting device. This Address points to the first two sequential bytes of a table containing the Address of the service routine.

When the DMA is the interrupting device, it will place its special low-byte vector Address on the Data Bus when signals "IORQ\*" and "Ml\*" are both asserted.

Pin 10 of DMA U20 will become an output line when the DMA has taken control of the System Buses. As an output signal, an asserted "IORQ\*" indicates that the lower half of the Address Bus holds a valid Port Address for another I/O device involved in a DMA transfer of data. In this application, it will be one of the Port Addresses such as those of the FDC.

SELECT\*

To Pin 2/1 of U39 and to Pin 43 of the Model II System Bus (see same, Sheet 3).

MREQ\*

From Pin 12 of the DMA. This signal indicates that the Address Bus holds a valid Address for a Memory Read or Write operation from the CPU. When the DMA has control of the System Buses, this signal indicates that the DMA is requesting a transfer of data to, or from Memory.

RD\* DMA From Pin 9 of the DMA. This is a bi-directional line. As an input line, this signal indicates that the CPU wants to read the Status Bytes from the DMA's Read Registers. This line will become an output after the DMA has taken control of the System Buses. As an output, this signal will indicate a DMA-controlled Read from a Memory or Port Address.

WR\* DMA From Pin 8 of the DMA. This is a bi-directional line. As an input line, this signal indicates that the CPU wants to write Control, or Command Bytes to the DMA Write Registers. This line will become an output after the DMA has taken control of the System Buses. As an output, this signal will indicate a DMA-controlled Write to a Memory or Port Address.

BAI\*

To Pin 14 of the DMA. This line is labled "BUSAK\*" (see same). This signal, when asserted, is an indication to the DMA that the System Buses have been released for DMA control. See signal "BAO\*".

**KBINT**

Inappropriately shown on Sheet 1, Pin 42 of the Model II System Bus, since it is on Sheet 3 properly labeled as KBIRQ\* (see same).

INTRQ\*

(BUS)

From Pin 11 of the Model II System Bus. To Pin 2 of U4, where it is used to assert an off-board Interrupt from the PIO/FDC, or other add-on devices such as HD, ARCNET, etc. configured in the interrupt daisy chain.

NMIRQ\*

From Pin 12 of the Model II System Bus. To Pin 17 of U12. This signal sources from the 30KHz Real Time Clock on the VDG, directing the Z80A to the Real Time Clock Service Routine vectored at 0066H in RAM.

8MHz

From Pin 8 of U3Ø to Pin 46 of the Model II System Bus for use in pre-comp on the FDC Board. U3Ø is improperly drawn as a NOR gate: it is a NAND gate.

#### CPU Board Test Points

- TP 1 From Pin 10 of U1/1. This is the 4 MHz System Clock.

- TP 2 From Pin 5 of U2/1. This is a 2 MHz signal used at Pins 21, 22, and 23 of CTC U19/2.

- TP 3 "ROMØCE\*".....From Pin 6 of Ul6/3.

- TP 4 "READ\*".....From Pin 8 of U3/3.

- TP 5 "8 MHZ".....From Pin 6 of U3Ø/1.

- TP 6 "CE\*".....From Pin 4 of U4/1.

- TP 7 "CLOCK"......From Pin 12 of U1/1.

- TP 8 "BUSRQ\*".....From Pin 15 of U2Ø/1.

- TP 9 "CECTC\*"......From Pins 1, 2, 3, and 4 of U36/3.

- TP 10 "CESIO\*".....From Pins 5, 6, 7, and 9 of U36/3.

| TP | 11 | "RESET*" | .From | Pin 4 | 4 oÈ | 1129/2.   |

|----|----|----------|-------|-------|------|-----------|

|    |    |          |       |       | 7 UL | UZ 31 Z . |

- TP 12 "WAIT\*".....From Pin 3 of U14/2.

- TP 13 "INTAK\*".....From Pin 11 of U21/3.

- TP 14 This test point is not listed.

- TP 15 "SELECT\*"......From Pin 11 of U14/3.

- TP 16 From Pin 8 of U4/3.

A logic high at this test point is an indication that the Data Drivers of U32/3 and U31/3 are enabled.

TP 17 From Pin 8 of U22/3.

A logic low at this test point is an indication that the Data Receivers of U32/3 and U31/3 are enabled.

TP 18 "ROM\*/RAM".....From Pin 8 of Ul3/2.

# – TRS-80 ® ——

CPU Board Port Allocation Table

| Port No. | Allocation       | Function                 |

|----------|------------------|--------------------------|

| FØH      | стс              | Channel Ø                |

| F1H      | стс              | Channel 1                |

| F2H      | стс              | Channel 2                |

| F3H      | стс              | Channel 3                |

| F4H      | SIO A            | Channel A data           |

| F5H      | SIO B            | Channel B data           |

| F6H      | SIO A            | Channel A Command/Status |

| F7H      | SIO B            | Channel B Command/Status |

| F8H      | DMA              | DMA Command/Status       |

| F9H      | ROM ENABLE LATCH | ENABLES/DISABLES ROM     |

CPU Board Jumper Options And Notes

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

Schematic: The jumper terminals on the schematic are not labeled.

REV A Board: The jumper terminals on this Board are not labeled.

REV B Board: The jumper terminals on this Board are not labeled.

REV C Board: The jumper terminals on this Board are labeled A, B, C, etc. The labels, however, appear only on the later production runs of this Board.

Note: Some of the labeled REV C Boards have labels "A" and "B" referenced to the wrong pads.

Refer to the drawing on page 1-21 for the correct pad locations.

REV D Board: The jumper terminals on this Board are labeled EØ, E1, E2, etc. Three jumper options have been deleted from this Board:

- The 2/4 MHz System Clock option is now permanently wired for a System Clock of 4 MHz. The stake pins at Terminals A and B have been removed, and the terminal pads are now bridged with foil. These pads are not labeled.

- 2. The 4/8 MHz precomp option is now permanently wired for a precomp of 8 MHz. The stake pins at Terminals U and V have been removed and the terminal pads are now bridged with foil. The pads are still labeled.

- 3. The SIO Channel B External/Internal Receiver-Transmitter Clock option is now permanently wired to the internal clock sourced from the CTC. The stake pins at Terminals E14 and E15 have been removed, and the terminal pads are now bridged with foil. The pads are still labeled.

# TRS-80 ® -

#### CPU Board Standard Jumper Configuration

| A - B     | 4 MHz System Clock.                                         |

|-----------|-------------------------------------------------------------|

| u - v     | 8 MHz Precomp Clock.                                        |

| E7 - E8   | SIO Channel A Receive Clock.<br>Sourced from the CTC.       |

| E11 - E12 | SIO Channel A Transmit Clock.<br>Sourced from the CTC.      |

| E14 - E15 | SIO Channel B Receive/Transmit Clock. Sourced from the CTC. |

CPU Board Jumper Configuration

For BISYNC Operation

Note: The CPU Board must be modified for BISYNC operation. Refer to Model II Technical Bulletin II:17 for the modification procedure.

| E6 - E7   | SIO Channel A Receive Clock.<br>Sourced from external device.  |

|-----------|----------------------------------------------------------------|

| E1Ø - E11 | Channel A Transmit Clock.<br>From CTC to external device.      |

| E9 - E12  | SIO Channel A Transmit Clock.<br>Sourced from external device. |

#

####

#### Jumper Terminal Cross Reference REV C and REV D CPU Boards

####

| REV C | REV D      | Source/Destination                     |

|-------|------------|----------------------------------------|

| N     | ЕØ         | From Pin 8 of U21/2.                   |

| P     | El         | To Pin 4 of U14/2.                     |

| М     | E2         | From R12. +5 volt pull-up              |

| S     | E3         | From Pin 9 of U13/2.                   |

| T     | E4         | To Pin 5 of U22/2 and Pin 10 of U21/2. |

| R     | <b>E</b> 5 | From RlØ. +5 volt pull-up              |

| L     | <b>E6</b>  | From Pin 11 of U10/2.                  |

| J     | E7         | To Pin 13 of U18/2.                    |

| K     | E8         | From Pin 7 of Ul9/2.                   |

| Н     | E9         | From Pin 8 of UlØ.                     |

| F     | E1Ø        | To Pins 12 and 13 of U7/2.             |

| G     | E11        | From Pin 8 of Ul9/2.                   |

| I     | E12        | From Pin 14 of U18/2.                  |

| D     | E13        | From Pin 6 of U9/2.                    |

| С     | E14        | From Pin 9 of CTC U19/2.               |

| E     | E15        | To Pin 27 of SIO U18/2.                |

| A     | A          | To Pin 3 of U2/1.                      |

| В     | В          | From Pin 9 of U28/1.                   |

| U     | U          | To Pin 9 of U3Ø/1.                     |

| v     | V          | From Pin 8 of U29/1.                   |

TRS-80 ®

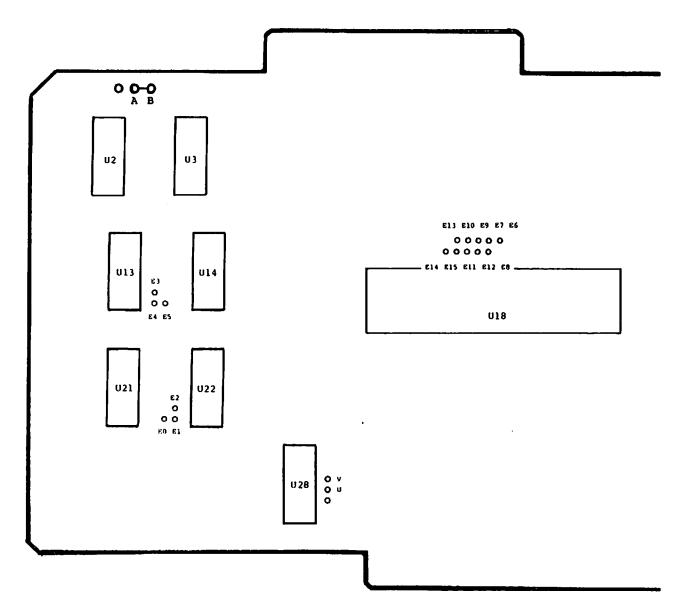

CPU Board Jumper Terminal Locator

The physical location of the jumper terminals illustrated above are identical for all Board revisions.

The labels shown are those of the REV D Board.

| ***** | ******* | ***** | ***** |

|-------|---------|-------|-------|

|-------|---------|-------|-------|

#### Section Two

#### Model II FDC Board - Early

#### \*\*\*\*\*\*\*\*\*\*\*\*\*

#### Contents

| Glossary - Sheet 1              | 2-3  |

|---------------------------------|------|

| Glossary - Sheet 2Page          | 2-27 |

| Test Point DefinitionsPage      | 2-32 |

| Jumper ConfigurationPage        | 2-35 |

| Mother Board Interrupt LoopPage | 2-36 |

The listings in this glossary are divided into 2 sections, respective to the 2 sheets of the Early FDC Board schematic.

When a signal from one sheet is referenced to another, a pointer, "/#", will be used to indicate the sheet: i.e. From Pin 9 of U14/2 To Pin 24 of U6/1.

REV D is the last revision of the old style FDC Board. The schematics contained in the manual reflect the circuits which are on the REV C Board. Some of the circuits changes between the different old style FDC Boards will be pointed out in the glossary.

# Index for Early FDC Board Signals

| Signal     | Page | Signal    | Page |

|------------|------|-----------|------|

| 2 MHZ      | 2-23 | INTRQI*   | 2-31 |

| 8 MHZI     | 2-8  | IOCYCI*   | 2-7  |

| B/A*       | 2-27 | IORQI*    | 2-31 |

| BUSY       | 2-29 | IP*       | 2-14 |

| C/D*       | 2-28 | LATE      | 2-20 |

| CEFDC*     | 2-5  | MR*       | 2-18 |

| CEPIO*     | 2-5  | OUT*      | 2-1Ø |

| CLOCK      | 2-27 | PACK*     | 2-30 |

| CLOCKI     | 2-27 | PE        | 2-29 |

| CLK        | 2-18 | PRIME     | 2-28 |

| CPUIN      | 2-7  | PSEL      | 2-29 |

| CWD        | 2-21 | PSTB*     | 2-3Ø |

| DIR        | 2-13 | RAW DATA  | 2-23 |

| DISKCHANGE | 2-28 | RCLK      | 2-18 |

| DRQ        | 2-18 | RDA       | 2-22 |

| DRVSLT*    | 2-6  | RDY       | 2-15 |

| EØ*-E7*    | 2-3  | READ DATA | 2-22 |

| E8*-EF*    | 2-3  | READI*    | 2-7  |

| EARLY      | 2-20 | RESETI*   | 2-8  |

| EF*        | 2-4  | SELECTI*  | 2-6  |

| EX*        | 2-3  | STEP      | 2-13 |

| FAULT      | 2-29 | SYNCI*    | 2-8  |

| FM/MFM*    | 2-12 | TG43      | 2-11 |

| HLD*       | 2-16 | TRKØ      | 2-14 |

| HLT        | 2-16 | TWOSIDED  | 2-28 |

| IEIN       | 2-11 | WD        | 2-14 |

| IEOUT      | 2-11 | WG        | 2-13 |

| IN*        | 2-9  | WPRT*     | 2-14 |

| INTAK*     | 2-1Ø | WRITEI*   | 2-7  |

| INTRQ      | 2-19 | XF*       | 2-3  |

|            |      |           |      |

#### Glossary - Sheet 1

Only the mnemonics originating from Sheet 1 of the Early FDC schematic will be covered under this heading.

XF\*

From Pin 8 of U20. This signal decodes the low-order address nibble as FH when A01-A31 are all logic high. "XF\*" goes to Pin 12 of U8, where it is NANDed with signal "E8\*-EF\*" to produce signal "EF\*" (see same). Pins 6/8 of U20 are shown reversed on the schematic.

EX\*

From Pin 6 of U20. This signal decodes the upper address nibble, or first half of the FDC Port Addresses, as EH to access Ports E0-EF. See page 2-5 for a functional summary of Ports allocated to the FDC Board.

Signal "EX\*" is used at Pin 9 of Ul9 and Pin 1 of U8. U8 and Ul9 are used as steering gates for signal "EX\*", and are controlled by the logic status of Address line A3. When Address line A3 is a logic high, "EX\*" will be steered through Ul9 to produce signal "E8\*-EF\*" (see same). Conversely, when Address line A3 is at a logic low, "EX\*" will be steered through U8 to produce signal "EØ\*-E7\*" (see same).

E8\*-EF\*

From Pin 8 of U19. This signal will be asserted when the CPU is in the process of accessing Ports E8 through EF. "E8\*-EF\*" is applied to Pin 13 of U8 where it is NANDed with "XF\*" to produce signal "EF\*" (see same).

EØ\*-E7\*

From Pin 3 of U8. This signal will be asserted when the CPU is in the process of accessing Ports E $\emptyset$ -E7.

"EØ\*-E7\*" is used at:

\* Pin 9 of U8 where it is NANDed with a logic low Address A2 to produce signal "CEPIO\*" (see same). Signal "CEPIO\*" will be asserted when the CPU is in the process of accessing Ports EØ through E3.

- \* Pin 4 of U8 where it is NANDed with a logic high Address A2 to produce signal "CEFDC\*" (see same). Signal "CEFDC\*" will be asserted when the CPU is in the process of accessing Ports E4 through E7.

- \* Pin 5 of U19 where it is NANDed with an asserted signal "IN\*" to produce a logic low at Pin 6.

Pin 6 will be at a logic low only when the CPU is in the process of performing a Read operation at Ports EØ through E7. During this Read operation, the logic low appearing at Pin 6 will be ORed through UlØ, then inverted at Pin 8 of Ul8 to produce signal "CPUIN" (see same). "CPUIN" is used to enable the Data Drivers of U32 and U33.

Note: The output of U1Ø (Pin 6) is also used at Pin 5 of U11/2 where it is ANDed with signal "CEPIO\*" to enable the Data Drivers of U12 and U23. This additional output from Pin 6 of U1Ø is not shown on the schematic.

\* Pin 10 of U10, where it is ORed through to appear at Pin 9 of U21. Pin 10 of U21 will be at a logic low whenever the CPU is in the process of accessing any Port. The logical product of the two inputs to U21 will be used to control the logic status of signal "SELECTI\*" (see same). In this application, "SELECTI\*" will be asserted only when the CPU is in the process of performing a Read/Write operation at Ports E0 through E7.

EF\* From Pin 11 of U8. This signal will be asserted when the CPU is in the process of accessing Port EF.

"EF\*" is used at Pin 5 of U21 where it is NANDed with signal "OUT\*" (see same) to produce signal "DRVSLT\*" (see same). Signal "DRVSLT\*" will be asserted only when the CPU is in the process of performing a Write operation at Port EF.

Signal "EF\*" is also used at Pin 9 of UIØ where it is ORed with EØ\*-E7\* (see same) to appear at Pin 9 of U21. Pin 1Ø of U21 will be at a logic low whenever the CPU is in the process of accessing any Port.

The logical product of Pins 9 and 10 of U21 will be used to control the status of signal "SELECTI\*" (see same). In this application, "SELECTI\*" will be asserted only when the CPU is in the process of performing a Write operation to Port EF.

| PORT # | ALLOCATION              | FUNCTION                    |  |

|--------|-------------------------|-----------------------------|--|

| ЕФН    | PIO Port A Data         | Printer and FDC INT.        |  |

| E1H    | PIO Port 8 - Data       | Printer Data (output)       |  |

| E2H    | PIO Port A - Control    | · Configuring Port A        |  |

| E3H    | PIO Port B - Control    | Canfiguring Port B          |  |

| Е4Н    | FDC Status/CMD Register | FDC Status and CMD .        |  |

| E5H    | FDC Track Register      | Current Track Add.          |  |

| E6H    | FDC Sector Register     | Current Sector Add.         |  |

| E7H    | FDC Data Register       | Data To or From<br>Diskette |  |

| EFH    | Orive Select Latch      | Drive, Mode, Side<br>Select |  |

CEPIO\* From Pin 8 of U8. To Pin 4 of PIO U22/2. This is (TP 18) Chip Enable signal for the PIO.

The PIO will be selected when this signal is at a logic low. This selection will allow the CPU to communicate with the PIO. Communication with this chip will be in progress when the CPU is addressing Ports EØ through E3. The functional allocation of each of these Ports is listed above.

"CEPIO\*" is also used at Pin 6 of Ull/2 where it is ANDed with the logic low at Pin 5. Pin 5 of Ull will be at a logic low when the CPU is in the process of performing a Read operation at Ports EØ through E7. The result of this input combination will cause the Data Drivers of Ul2/2 and U23/2 to be enabled only when the CPU is in the process of performing a Read operation at PIO Ports EØ through E3.

CEFDC\* From Pin 6 of U8. To Pin 3 of FDC U6. This is the (TP 14) Chip Enable signal for the FDC.

# TRS-80 <sup>®</sup>

The FDC chip will be selected when this signal is at a logic low. This selection will allow the CPU to communicate with the FDC. Communication with this chip will be in progress when the CPU is addressing Ports E4 through E7. The functional allocation of each of these Ports are listed on Page 2-5.

DRVSLT\*

From Pin 6 of U21. Signal "DRVSLT\*" will be asserted only when the CPU is in the process of performing a Write operation to Port EF.

"DRVSLT\*" is used at Pin 9 of Ul7 to latch the logic status of the following signals.

\* Drive Select.

A logic high at Pin 2, 5, 7, or 10 of Ul7 will select one of four drives: "DS1\*", "DS2\*", DS3\*", or "DS4\*". Only one of these signals should be asserted at any one time.

\* Side Select.

A logic high at Pin 15 of U17 will select Side  $\emptyset$  of the diskette. Signal "SDSEL" at Pin 8 of U16 will be at a logic low with this selection.

\* Double Density Select.

A logic low at Pin 12 of U17 will select the Double Density mode. This signal is labeled "FM/MFM\*" (see same), and goes to "30 Pin 1 U29 Pin 10, and U6 Pin 37.

SELECTI\*

From Pin 8 of U21. This signal will be asserted when the CPU is in the process of performing a Read/Write operation at Ports EØ through E7, and EF.

"SELECTI\*" is routed to Pin 3 of U34/2, then further to Pin 43 of the Model II System Bus.

Note: This signal is produced by all of the original Model II Boards (this excludes the revised FDC Board). Each Board has this signal tied to Pin 43 of the Model II System Bus (wired AND). "SELECTI\*" is not used, and it's intended purpose is unknown. It functions as a "Board Busy" signal, since it is activated only when the CPU is in the process of performing a Memory Read/Write or I/O operation.

#### **CPUIN**

From Pin 8 of U18. This signal will be asserted when the CPU is in the process of performing a Read operation at Ports EØ through E7. "CPUIN" will also be asserted when the CPU is in the process of servicing an Interrupt Request from the PIO.

"CPUIN" is applied to Pins 1 and 15 of U32/2 and U33/2. The logic high at Pins 1 and 15 is used to enable the Data Drivers of these bi-directional Buffers.

#### WRITEI\*

From Pin 18 of Buffer U36. This signal will be asserted when the CPU is writing to a Memory Address or an I/O Port.

"WRITEI\*" is used at Pin l of U2l where it is NANDed with "IOCYCI\*" to produce signal "OUT\*" (this signal is not labeled).

#### IOCYCI\*

From Pin 16 of Buffer U36. This signal will be asserted when the CPU is writing or reading any I/O Port. "IOCYCI\*" will also be asserted when the CPU is acknowledging an Interrupt Request.

"IOCYCI\*" is used as outlined below.

- \* At Pin 2 of U21 where it is NANDed with "WRITEI\*" to produce "OUT\*" (see same). "OUT\*" is not labeled.

- \* At Pin 13 of U21 where it is NANDed with "READI\*" to produce "IN\*" (see same). "IN\*" is not labeled.

- \* At Pin 2 of Ul9 where it is NANDed with "SYNCI\*" to produce "INTAK\*" (see same).

- \* At Pin 36 of PIO U22/2 where it is called "IORQ\*" (see same).

#### READI\*

From Pin 5 of Buffer U36. This signal will be asserted when the CPU is performing a Read at any Memory Address or I/O Port. It is NANDed at Pin 12 of U21 with signal "IOCYCI\*" (see same) to produce signal "IN\*" (see same). Signal "READI\*" is also used at Pin 35 of PIO U22/2 where it is called "RDI\*" (see same).

SYNCI\*

From Pin 3 of Buffer U36. "SYNCI\*" is the Ml\* signal produced by the CPU during an Op-code Fetch cycle, or an Interrupt Acknowledge.

"SYNCI\*" is used at Pin 1 of U19 where it is NANDed with "IOCYCI\*" to produce signal "INTAK\*" (see same).

"SYNCI\*" is also used at Pin 1 of U10/2 where it is ORed with "RESETI\*" to Pin 37 of U22/2. The signal at Pin 37 of the PIO is called "M1\*" (see same).

RESETI\*

From Pin 14 of Buffer U36. This is the System Reset signal which is initiated during a Power On or Manual Reset cycle.

"RESETI\*" is used at Pin 19 of FDC U6 where it is called "MR\*" (see same).

Signal "RESETI\*" is applied to Pin 1 of U17 where it is used to clear the outputs of this latch. Note: The "CLR" input to U17 is Pin 1. Label it. Also, the Pin 1 input should show an inversion bubble: draw it in.

"RESETI\*" is also used at Pin 2 of U10/2 where it is ORed with "SYNCI\*" to Pin 37 of U22/2. The signal at Pin 37 of the PIO is called "MI\*" (see same).

8MHZI (TP 17) From Pin 9 of U36. This is the 8 MHz clock from the CPU Board. It is used at Pin 9 of Ul to clock through the logic status of signal "WD" (see same).

Note 1: The four parts of Ul are wired as a shift register which is clocked at 8 MHz. This arrangement provides a predictable 125 nanosecond delay per stage for the logic high of

"WD" appearing at Pin 4 of Ul. Ul is part of

the Write Precompensation logic.

The three delayed outputs of Ul are used at U2 along with the "EARLY" and "LATE" signals from Pins 11 and 8 of U7. The logical result of this combination will produce write precompensated signals at Pins 7 and 9 of U2. The Write Precompensated pulses appearing at Pin 7 of U2 will have a 125 nanoseconds shift, and those at Pin 9, a 250 nanosecond shift.

- Note 2: The steering logic consisting of four parts of U3 is programmed to allow only the 250 precompensated pulses to pass through to One-Shot U37. This steering is controlled by the position of Jumpers 6, 7, and 8. The normal System configuration is to have 6 and 7 jumpered for 250 precompensation. The jumper between 7 and 8 shown on the schematic is incorrect.

- Note 3: The precompensated write pulse appearing at Pin 1 of U3 is used as a trigger at Pin 10 of One-Shot U37. The purpose of this one-shot is to ensure that the pulse width of the write data pulses will always be at approximately 250 nanoseconds. This output pulse is inverted at Pin 4 of U16 (TP 10) to become signal "CWD" (see same).

- Note 4: U37 mentioned in Note 3, appeared as a wired mod, or as a piggyback module on the Rev Blank, A, and B Boards. The Rev C and D Boards have this one-shot circuit incorporaed into the Board design.

IN\* From Pin 11 of U21. This signal is not labeled on the schematic. "IN\*" is the logical product of signals "READI\*" and "IOCYCI\*", and it will be asserted when ever the CPU is in the process of reading any I/O Port Address.

"In\*" used at Pin 4 of Ul9 where it is NANDed with "EØ\*-E7\*" to produce a logic low at Pin 6 of Ul9. This low at Pin 6 is ORed through UlØ, then further, to be inverted at Pin 8 of Ul8 to become signal "CPUIN" (see same).

When signal "IN\*" is asserted, the logic low appearing at Pin 6 of UlØ is also used at Pin 5 of Ul1/2. If "CEPIO\*" is asserted at Pin 6 at this same time, the logical product of these two signals will enable the Drivers of Ul2/2 and U23/2 for a CPU Read of the PIO.

Note 1: The signals of the Address and Data lines of the Model II System Bus travel between the Boards in inverse logic: i.e., a logic high on a Board will appear as a logic low on the Bus.

- Radio ∫haek<sup>®</sup>

# TRS-80 <sup>6</sup>

Note 2: Buffers U12 and U23 mentioned above are electrically wired between the internal Data Bus of the FDC Board and the Data Input/Output lines of the PIO. These Buffers are used to invert the logic levels of the data going to, and coming from the PIO chip. This correction is necessary because the internal data Bus of the FDC Board is wired for inverse logic.

Signal "IN\*" is also ORed with "OUT\*" through UlØ, then appears at Pin lØ of U21 where it is NANDed with the FDC Port signals "EØ\*-E7\*" or "EF\*" to generate signal "SELECTI\*" (see same).

"IN\*" is used again at Pin 4 of FDC U6 where it is called "RE\*". This is the Read Enable signal to the FDC chip. A logic low at this input will cause the FDC to gate out data from a selected Register when the Chip Select signal at Pin 3 is at a logic low.

OUT\*

From Pin 8 of U21. This signal is not labeled on the schematic.

"OUT\*" is the logical product of signals "WRITEI\*" and "IOCYCI\*", and it will be asserted when ever the CPU is in the process of writing to any I/O Port Address.

Signal "OUT\*" is used as follows.

- \* At Pin 4 of U21 where it is NANDed with "EF\*" to produce signal "DRVSLT\*" (see same).

- \* At Pin 12 of U10 where it is ORed with "IN\*" to appear at Pin 10 of U21. It is NANDed with "E0\*-E7\*" or "EF\*" to generate signal "SELECTI\*" (see same).

- \* At Pin 2 of FDC U6 where it is called "WE\*". This is the Write Enable signal to the FDC chip. A logic low at this input will allow the CPU or DMA to gate in data into the selected Register when the Chip Enable signal is asserted at Pin 3.

INTAK\*

From Pin 3 of Ul9. This signal is the logical product of "SYNCI\*" and "IOCYCI\*", which are Ml\* and IORQ\* on the CPU Board. It will be asserted when the CPU is in the process of servicing, or acknowledging an Interrupt Request.

**TG43**

# TRS-80®

In this application, the NANDed result of "INTAK\*", "IEIN" (see same), and "IEOUT" (see same) through Ul3 will be used to enable the Data Drivers of Ul2/2, U23/2, U32/2, and U33/2.

Note: The logic high at Pin 2 of Ul3 is an indication that a device of higher priority has not generated an Interrupt Request. The logic high on Pin 13 of Ul3, on the other hand, is an indication that the PIO has generated an Interrupt Request. From this we can see that the Drivers mentioned above will only be enabled when the Interrupt Request of the PIO is in the process of being serviced by the CPU.

IEIN From Pin 13 of the Model II System Bus. To Pin 2 of Ul3 and Pin 24 of the PIO. For a functional understanding of this signal refer to the note under "INTAK\*" and also to the diagram on page 2-36.

IEOUT From Pin 14 of the Model II System Bus. To Pin 5 of U16 and Pin 22 of the PIO. For a functional understanding of this signal refer to the note under "INTAK\*" and also to the diagram on page 2-36.

From Pin 29 of FDC U6. This signal will be asserted between Tracks 44 through 76 in the Double Density or Single Density modes.

"TG43" is inverted at Pin 6 of U16, then onward to Pin 2 of the Drive Bus. "TG43" is used to reduce the write current of the drive by approximately 25% when the head is positioned between tracks 44 through 76. The peak-to-peak write current for an 8-inch drive before Track 44 is about 10 milliamperes.

Signal "TG43" is also used at Pin 5 of U7 where it is ANDed with "FM\*/MFM" (see same) to enable two parts of U7. The enabling of these gates will allow the "EARLY" (see same) and "LATE" (see same) signals to pass through to U2 for Write Precompensation.

Note 1: When the drive head is positioned on a track less then 43, "TG43" will be negated and block the "EARLY" and "LATE" signals at Pin 5 of U7.

# Radio Shaek

Note 2: During the time that "TG43" is negated, the Write Data will be sourced from Pin 7 of Ul.

#### FM/MFM\*

From Pin 12 of Ul7. This is the Density Mode Enable signal. A logic low will enable the Double Density mode. This mode will be selected when the CPU does a Write to Port EF with data bit 7 at Pin 13 of Ul7 at a logic low.

When the Double Density mode is selected, "FM/MFM\*" will be used as indicated below.

- \* At Pin 37 of FDC U6. A logic low at this input will set the interface logic of the FDC and enable the Double Density circuits of the chip.

- \* At Pin 4 of U7 where it is ANDed with "TG43" to gate through the precompensation signals "EARLY" and "LATE" to U2. See "TG43" for supporting information.

- \* At Pin 10 of U29 where it is used to disable the Single Density mode 500 KHz signal at Pin 9. Refer to the second note below.

- \* At Pins 1 and 2 of U3Ø where it is inverted at Pin 3 to place a logic high at Pin 5 of U3Ø. Refer to the second note below.

The low at Pins 1 and 2 of U3Ø is also used to turn on Transistor Q2. Q2 will place Potentiometer R37 in parallel with Potentiometer R36.

- Note 1: Potentiometers R36 and R37, along with Potentiometers R32 and R5, should be adjusted only as outlined in the FDC Board alignment procedure, FDCALG.

- Note 2: The two parts of U29 will divide the 2 MHz VCO signal appearing at Pin 6 of U27, by 2 and by 4, respectively. The 1 MHz signal at Pin 5 of U29 will appear at Pin 8 of U30 when the Double Density mode is enabled (this is due to the low on Pin 10 of U29 and the high on Pin 5 of U30). When the Single Density mode is enabled, Pin 10 of U29 will be high and Pin 5 of U30 low

and the 500 KHz signal now appearing at Pin 9 of U29 will be routed through to Pin 8 of U30.

The signals (SD=500 KHz, DD=1 MHz) at Pin 8 of U30 are used at U28 of the Clock Recovery circuit.

The signals at Pin 8 of U3Ø will be divided again at Pin 5 of Ul4 to become the nominal Clock Recovery frequencies (DD= 5ØØ KHz, SD=25Ø KHz) for the FDC through U4 and U7.

WG

From Pin 30 of FDC U6. This is the Write Gate signal to the drive. "WG" will be set to a logic high approximately 2 microseconds before an actual Write operation in the FM mode. In the MFM mode, it will be set to a logic high approximately 1 microsecond before the actual Write.

The Write Gate signal is inverted at Pin 12 of U4 to become signal "WG\*". "WG\*" is tied to Pin 40 of the Drive Bus.

DIR

From Pin 16 of FDC U6. This is the Head Direction to the Drive logic. "DIR" works in conjunction with signal "STEP" (see same). Signal "STEP" will position the head inward, or towards Track 76 when "DIR" is at a logic high, and will position the head outward, or towards Track Ø, when "DIR" is at a logic low. The direction signal will appear on the Drive Bus approximately 12 microseconds before the first step pulse is executed.

The direction signal is inverted at Pin 12 of U5 to become signal "DIR\*". "DIR\*" is tied to Pin 34 of the Drive Bus.

STEP

From Pin 15 of FDC U6. This is a 2 microsecond positive-going pulse, used to move, or position the drive head over the diskette media. For every step pulse executed by the FDC, the drive head will move one track location in the direction determined by the logic status of signal "DIR" (see same). The first step pulse will appear approximately 12 microseconds after signal "DIR" becomes asserted.

The step pulse is inverted at Pin 2 of U4 to become signal "STEP\*" (TP 12). "STEP\*" is tied to Pin 36 of the Drive Bus.

WPRT\*

From Pin 44 of the Drive Bus. To Pin 36 of FDC U6.

"WPRT\*" is the Write Protect signal from the drive. The Write Protect signal is used by the FDC to determine if the diskette in use is write protected. The status of this input signal will be sampled whenever the FDC receives a write command. A logic low at this input will set the write protect bit (bit 6) in the Status Register of the FDC.

IP\*

From Pin 20 of the Drive Bus. To Pin 35 of FDC U6.

"IP\*" is the Index Pulse from the drive. It is used to inform the FDC chip when the index hole is encountered on the diskette. This pulse should appear every 166.67 milliseconds after the drive spindle has come up to speed. The Index Pulse is used in the FDC to synchronize various command operations. Refer to the FD179x spec sheet for the details on how this signal is used.

TRKØ\*

(TP 4)

From Pin 42 of the Drive Bus. To Pin 34 of FDC U6. This is the Track  $\emptyset$  signal. A logic low at this input is used to inform the FDC that the drive head is positioned over Track  $\emptyset$ .

WD

From Pin 31 of FDC U6.

"WD" is the Write Data Pulse signal to the drive. The Write Data is a serial train of bits representing address marks as well as data and clock information in both the FM and MFM formats. Each bit of the pulse train will be made up of 200 nanosecond pulses (for DD) or 500 nanosecond pulses (for SD).

"WD" is used at Pin 4 of U1. The four parts of U1 are wired as a Shift Register. The output stages will introduce delays of 125, 250, 375, and 500 nanoseconds. These delays are used as outlined on the next page.

# TRS-80 <sup>6</sup>

\* Pin 7 of U2. The "125" shift.

The input signals to U2 for the "125" are:

- Pin 2 of Ul. This is the 125 nanosecond delay, and it is used as the NOMINAL Write Data signal.

- 2. Pin 4 of Ul. This is the zero delay, and it is used as the EARLY Write Data signal.

- 3. Pin 7 of Ul. This is the 250 nanosecond delay, and it is used as the LATE Write Data signal.

- \* Pin 9 of U2. The "250" shift.

The input signals to U2 for the "250" are:

- Pin 7 of Ul. This is the 250 nanosecond delay, and it is used as the NOMINAL Write Data signal.

- 2. Pin 4 of Ul. This is the zero delay, and it is used as the EARLY Write Data signal.

- Pin 15 of Ul. This is the 500 nanosecond delay, and it is used as the LATE Write Data signal.

The Nominal and/or Precompensated Write Data bits appearing at Pin 1 of U3 can be sourced from Pin 7 of U2 (with Terminals 7 and 8 jumpered for the 125 nanosecond shift) or from Pin 9 of U2 (with Terminals 6-and 7 jumpered for the 250 nanosecond shift). See signals "CWD" and "8MHZI" for supporting information.

RDY

To Pin 32 of FDC U6. This input to the FDC chip is used to indicate the readiness of the disk drive. This signal must be at a logic high before any of the read or write commands to the FDC can be executed. There are some exceptions: see signal "MR\*", also, the spec sheet on the FD179x.

The exact variables involved to produce this signal will depend on the type of drive in use. A few of the things a drive COULD check before producing this signal are listed on the next page.

- \* Check if the drive is selected.

- \* Check that the drive door is closed.

- \* Check to see if the drive spindle is up to speed.

- \* Check for the presence of the diskette Index Pulse.

"RDY" is the inverted result of the Ready signal appearing at Pin 22 of the Drive Bus.

#### HLD\* (TP 21)

From Pin 10 of U4. This signal is the inverted result of signal "HLD" at Pin 28 of FDC U6.

"HLD\*" is used to control the loading of the drive head against the diskette media. The drive head is loaded when this signal is asserted at a logic low.

The "HLD\*" signal is tied to Pin 18 of the Drive Bus. The negative-going edge of this signal is also used as a trigger at Pin 1 (label it!) of One-Shot U31. This one-shot is used to keep signal "HLT" (see same) negated for a period of approximately 75 milliseconds (the range specified in the service manual is 50 to 100 milliseconds).

Signal "HLD\*" is also used at Pin 1 of U16, which is part of the Raw Read Data Enable logic. Refer to signal "READ DATA" to see how this logic is enabled.

HLT

To Pin 23 of FDC U6. This is the Head Load Timing signal to the chip. The FDC chip will assume that the drive head is loaded, or engaged when this input signal switches to a logic high.

The initialization of this signal will be delayed with respect to the negative-going asserted edge of signal "HLD\*" by approximately 75 milliseconds. One-Shot U31 will introduce this delay whenever it is triggered by "HLD\*". This delay is necessary to allow the drive head to settle, or engage completely before the FDC does an actual Read or Write operation to or from the diskette media. See note on the next page.

Note: The Head Load Timing is a drive specification.

The head engagement time for most drives will

fall between the range of 30 to 100 milliseconds. U31 is used to set the HLT to an average

of approximately 75 milliseconds.

"HLT" is also used at Pin 4 of Ul3. Ul3 is part of the Raw Data Read Enable logic. Refer to signal "READ DATA" to see how this logic is enabled.

Note: The FDC will be able to read or write to the diskette only when signals "HLD" and "HLT" are true at Pins 28 and 23 of the FDC chip.

Pin 1 of FDC U6.

This Pin is not indicated on the block symbol of FDC, U6. Add the following to your schematic.

From the top of the block symbol, draw a zener diode symbol with its cathode end connected to ground. The anode of this zener should be shown tied to Pin 1 of the chip. This is a 2.7 volt zener.

- Note 1. According to the FD179x spec sheet, Pin 1 is internally connected to a back bias generator and should be left open. However, in the early days of the Model II, it was found that the FDC chip would become thermal at times. The problem was eventually isolated to the voltage at Pin 1: it was becoming too negative. The zener modification was introduced as a correction by clamping the voltage at Pin 1 to minus 2.7 volts. This zener should appear on the foil side of the Rev Blank, A, and B Boards. The Rev C, and D Boards have this zener (CR1) incorporated into the Board design.

- Note 2. When disk I/O problems are being encountered, don't hesitate to hook a scope probe to Pin l of the FDC chip. What you see there could tell you a lot about the chip. Make sure that the DC voltage level at this Pin is at minus 2.7 volts. Also, this voltage level should be clean, free of RF noise, or spikes. Don't guesstimate, just replace the FDC chip if it appears noisy.

MR\*

To Pin 19 of FDC U6. This is the Master Reset input to the FDC chip. A logic low will reset the FDC chip. A RESTORE (Ø3H) will be loaded into the Command Register, and the Not Ready Status bit will be reset during this time. The RESTORE command will be executed when this input returns to a logic high.

"MR\*" is controlled by signal "RESETI\*" (refer to this signal for supporting information) from Pin 14 of U36.

CLK (TP 13) To Pin 24 of FDC U6. This is the 2 MHz Master Clock input which is used by the chip as an internal timing reference.

The source of this input is labeled "OPTION PIN B" which originates from Terminal B on sheet 2 of the schematic. In the normal System configuration, Terminal B should be jumpered to Terminal A as indicated on the schematic. Refer to signal "CLOCKI" for supporting information.

RCLK (TP 23)

From Pin 3 of U7. To Pin 26 of FDC U6.

"RCLK" is used as the Data Recovery signal by the FDC. The nominal "RCLK" frequency is 500 KHz in the Double Density mode, and 250 KHz in the Single Density mode.

The two parts of U4 at the input to the FDC are used to decrease the duty cycle of the recovery clock by a slight percentage. This correction was probably done to compensate for the slight propagational delay introduced by U14 (at Pin 5). Note that the signals preceeding U14 are used for the actual clock recovery correction.

The basic function of the resultant "phase corrected", or adjusted "RCLK" is to latch in the read data input bits appearing at Pin 27 of the FDC. Refer to signals "FM/MFM\*", "READ DATA", and "RAW DATA" for supporting information.

DRQ (TP 15)

From Pin 38 of FDC U6. This is the Data Request signal from the FDC.

"DRQ" in normally kept at a logic low. It will be pulled to a logic high by Resistor RIØ when the Data Register of the FDC contains assembled data during a Read operation, or when the Data Register is

empty during a Write operation. The data request signal will switch back to a logic low after the DMA services the FDC by reading or loading the Data Register.

Signal "DRQ" is tied to Pin 11 of U34/2 where it is buffered at Pin 10 to become signal "XFERRQ". Note: Change "XFERRQI\*" at Pin 11 to "XFERRQI".

Signal "XFERRQ" is routed to Pin 41 of the Model II System Bus where it will travel back on the same Bus to Pin 41 of the CPU Board. "XFERRQ" is applied directly to Pin 25 of the DMA chip on the CPU Board. Pin 25 is the READY input to the DMA.

Note: Most data transfers from Drive-to-Memory or Memory-to-Drive are handled by the DMA. The DMA is used because its data transfer speed is much faster than the CPU.

The DMA can be programmed to operate in any of three modes: Byte, Burst or Continuous. The Byte mode is used for all DMA data transfers in the Model II. In this mode, the DMA and CPU will alternately share the System Bus during data transfer operations to and from the FDC. The time sharing of the System Bus during this period is called "interleaving". Interleaving allows the CPU to continue with its monitoring functions of the System.

The "XFERRQ" signal at Pin 25 of the DMA will be continuously monitored by this device to determine when the drive is ready for a read or write operation. When "XFERRQ" is asserted, the DMA will ask the CPU for control of the System Bus by generating signal "BUSRQ\*". Signal "BUSAK\*" is used to inform the DMA that the CPU has relinquished control of the System Bus.

INTRQ From Pin 39 (label it!) of FDC U6. This is the Inter(TP 13) rupt Request signal from the FDC chip. It is normally kept at a logic low. It will be pulled to a logic high by Resistor R14 at the completion of any command. It will switch back to a logic low after the Status Register is read, or the Command Register is written to.

"INTRQ" is tied to Pin 15 of PIO U22/2. Pin 15 is Bit Ø of the "A" Port of the PIO. The PIO is programmed to monitor the logic status of this bit. The PIO will generate an Interrupt Request to the CPU when the logic status of this bit switches to a logic high. The CPU will service this Interrupt Request (under the conditions outlined by signal "INTRQI\*") by executing a Read operation to Port EØ. The Status of all of the input lines of the PIO's "A" Port will be checked during this read. When this Read operation is in progress, the logic high of Bit Ø will inform the CPU that the FDC chip has generated an Interrupt Request. Upon completion of this Read to Port EØ, the CPU will perform another Read operation, but this time to Port E4 to check the bit levels of the FDC's Status register. The meaning of the Status bits in this Register will be a function of the type of command previously executed by the FDC.

**EARLY**

From Pin 17 of FDC U6. This is the early signal for Write Precompensation. When this signal is asserted along with the Write Data pulse appearing at Pin 31, signal "EARLY" will place a high at Pin 13 of U7. Pin 12 of U7 should already be at a high by the "FM\*/MFM" and "TG43" signals. The resulting high at Pin 14 of U2 will route the 1Cl input signal to the Pin 7 output and 2Cl input signal to the Pin 9 output. The signal appearing at Pin 7 will be the early precompensated write bit for the "125" mode: that at Pin 9 will be the same, but for the "250" mode. See signals "WD" and 8 MHZI" for supporting information.

LATE

From Pin 18 of FDC U6. This is the late signal for Write Precompensation. When this signal is asserted along with the Write Data pulse appearing at Pin 31, signal "LATE" will be used as a trigger at Pin 10 of of One-Shot U31. The one-shot will produce a positive-going pulse at Pin 5 (label this output line TP 30) when triggered. The width of the pulse will depend on the setting of Potentiometer, R5. Potentiometer R5 should be adjusted as outlined in the FDCALG procedure.

The waveforms associated with the R5 adjustment are illustrated on the next page. The pulse at TP 30 should have a period of approximately 2.5 microseconds after the R5 adjustment.

The positive pulse at Pin 5 of the one-shot will place a high at Pin 10 of U7. Pin 9 of U7 should already be at a high by the "FM\*/MFM" and "TG43" signals. The resulting high appearing at Pin 2 of U2 will route the 1C2 input signal to the Pin 7 output and the 2C2 input signal to the Pin 9 output. The signal appearing at Pin 7 will be the late precompensated write bit for the "125" mode: that at Pin 9 will be the same, but for the "250" mode. See signals "WD" and "8 MHZI" for supporting information.

CWD (TP 10) From Pin 10 of U4. This is the Compensated Write Data signal. A write bit transition will appear as a negative-going 250 nanosecond pulse. One-Shot U37 was added to the circuit to keep the widths of the write data bits consistent.

"CWD" is tied directly to Pin 38 of the drive Bus.

Note: Two types of FDC chips are used on this Board, the FD1791-02 from Western Digital, and the SY1791-02 from SYNERTEK.

The SY1791-02 is a second source for the FD1791-02. When it was introduced, problems with formatting past 43 began to appear. The cause was isolated to the EARLY pulse: it was ending sooner than the EARLY pulse of the FD1791-02. This early termination caused double pulses to appear on the Compensated Write Data. To correct this problem, a modification was made by tying the Write Data out (TP 10) to the Reset (Pin 1) of the shift register. This circuit addition allows the bit transition of the Write Data to clear the Shift Register, thus preventing double data pulse generation.

READ DATA From Pin 46 of the Drive Bus. This is the Raw Read Data from the drive. It will be gated through to Pin 6 of U13 (TP 9) only when the drive head is loaded and when the Head Load Timing delay has run out. This gating prevents the possiblity of reading garbage before the head has had time to settle on the diskette media. See signals "HLD\*" and "HLT" for supporting information.

RDA From Pin 13 of One-Shot U25 (label it!). This is the (TP 24) Raw Data Adjusted signal.

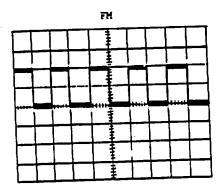

In the Single Density mode, a 2F pattern scoped at Pin 13 should display a 500 KHz square-wave as illustrated by the diagram below. Potentiometer R36 is used to set the duty cycle at 50%. This adjustment is outlined in the FDCALG procedure.

Timebase 1 usec/div

Channel A 2 V/div

Adjust for 50% duty cycle

The waveform of signal "RDA" in the Double Density mode is illustrated on the next page. Potentiometers R32 and R37 should be used to minimize the glitches.

Note: The settings of Potentiometers R5, R32, R36, and R37 are described in the FDCALG procedure.

Timebase l usec/div Vertical 2 v/div Invert 8 and add to A Minimize the glitches.

Signal "RDA" is used as a trigger at Pin 9 of One-Shot U25. This one-shot is used to generate the Raw Data pulse for the FDC chip. See "RAW DATA".

"RDA" is also used at U28, which is part of the Clock Recovery circuit.

RAW DATA

From Pin 12 of U25. Pin 12 will produce a negativegoing 200 nanosecond pulse with every data input transition.

The "RAW DATA" signal is routed to Pin 27 of FDC U6. The serial data stream appearing at this input will be latched (through the RCLK window) into the data Shift Register of the FDC. The FDC will execute signal "DRQ" (see same) when this Register is loaded.

2 MHZ (TP 26) From Pin 6 of VCO U27. This is the nominal 2 MHz RCLK frequency before it is divided by the two parts of U29, and the one part of U14. Pin 5 of U14 will output two different RCLK signals: 500 KHz for the MFM mode, and 250 KHz for the FM mode. These signals are used as the Recovery Clock for the FDC through U4 and U7. See signal FM/MFM\* for supporting information.

The Clock Recovery Circuits.

TP 26: The frequency of the square-wave signal appearing at this test point is controlled by the DC voltage at TP 25.

A voltage of 3.5 volts at TP 25 will set the nominal frequency of the VCO at TP 26 to 2 MHz.

Note: The 3.5 volts mentioned above is only an average. Do not use this voltage to set the VCO frequency. Follow the adjustment outlined in the FDCALG procedure.

TP 25: The voltage at this test point is used to set the frequency of the VCO. See TP 26. This voltage will vary from a low of about 1.6 volts, to a high of about 5 volts. The setting of Potentiometer R32 will determine the exact voltage. Diodes CR3 and CR4 are used to set the voltage limits at TP 25 to a low of -600 millivolts, and a high of +5.6 volts.

The voltage at TP 25 will always be lower than the voltage at Pin 6 of U26 by a factor of 0.45. This reduction factor is set by the resistance values of R34 and R35.

TP 5: Regulated +5 volts. This voltage is used as a supply source for VCO U27. It is also used to set the absolute upper voltage limit at TP 25 to +5.6 volts.

During initialization (power on), Capacitor C25 will charge through Diode CR2 to the +5.6 volt source of Zener, CR1. The 600 millivolt barrier potential of CR2 will limit the charge of C25 to +5 volts.

U26: In the "Insert Diskette" mode, the voltages at Test Points 27 and 28 should be at the logic zero level. In this state, the output voltage appearing at Pin 6 of U26 should be at about +8 volts (this assumes that the previous alignment on the FDC card was done correctly, and that the setting of R32 hasn't been touched. See TP 25 and TP 26). This voltage is an offset, produced by the current through Transistor Q1, and sensed at the input of U26.

If the voltage at Pin 6 of U26 appears abnormal, or does not vary when Potentiometer R32 is adjusted, check the voltage at the wiper of this potentiometer first. This voltage should vary from approximately -6.6 volts to -10 volts as the wiper is varied from one extreme to another. If the voltage does not change, check the potentiometer for bad connections. Also check Transistor Q1 to see if it is open.

If the potentiometer and transistor check good, then the operational amplifier should be checked next. Give this device a GOOD-BAD check by disconnecting the collector lead of Transistor Ql from the circuit. With the transistor electrically out, the voltage at Pin 6 of U26 should be at zero volts, +/- 200 millivolts (for this output indication to be true, TP 27 and TP 28 must both be at a logic low: check this to be sure). The operational amplifier should be considered bad if the voltage at this Pin is anything other than zero volts. Note: the output of a bad operational amplifier will usually latch to the plus or minus supply (+/- 12 volts).

----- TRS-80 <sup>®</sup> -

#### Glossary - Sheet 2

Only the mnemonics originating from Sheet 2 of the Early FDC schematic will be covered under this heading.

CLOCK

From Pin 44 of the Model II System Bus. This is the 4 MHz System Clock. It is buffered at Pin 2 of U34 to become signal "CLOCKI" (see same).

Note: U34 is an open collector device. It will open, or switch to a high Z state with a logic high. Resistor R51 (located on the left side of U22 on the schematic) is used to pull-up the line to +5 volts.

CLOCKI

From Pin 2 of Buffer U34. This 4 MHz signal is applied to Pin 25 of PIO U22. The PIO will use this clock to synchronize certain internal signals.

"CLOCKI" is also used at Pin 11 of U14 where it is divided by 2 to emerge at Pin 9 as a 2 MHz signal. This 2 MHz signal is tied to Terminal "A", which is jumpered to Terminal "B", then further to Pin 24 of FDC U6.

B/A\*

To Pin 6 of PIO U22. From Address line AØI.

This is the PIO "B" Port or "A" Port Select signal.

The logic status of this signal will define which