# COM 9032 Local Area Network Transceiver LANT

#### **FEATURES**

- ☐ Reduces chip count for COM 9026 ARCNET\* implementations by 6-8 TTL chips

- ☐ Performs all clock generation functions for the COM 9026

- ☐ Compatible with the COM 9026

- ☐ Provides line drive signals for transmission

- ☐ Converts incoming serial receive data to NRZ data format

- ☐ Generates two 4 MHz general purpose clocks

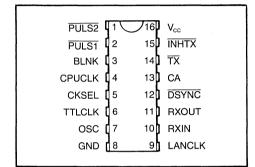

# PIN CONFIGURATION

# GENERAL DESCRIPTION

The COM 9032 local area network transceiver is a companion chip to the COM 9026 Local Area Network Controller (LANC) and will perform the additional functions necessary to allow simple interface to a transmission media for all ARCNET\* (or equivalent) local area networks. Using a 20 MHz input clock, the COM 9032 will produce two, 5 MHz clocks for the COM 9026. The first 5 MHz clock is free running and will directly feed the CLK input of the COM 9026 (pin 19). The second 5 MHz clock has start/stop capability which is controlled by the DSYNC output of the COM 9026 (pin 36) and the received data input as required by the COM 9026 (pin 2). Two additional 4 MHz free running clocks are also generated on the COM 9032 to allow operation of other logic, a microprocessor, or an LSI controller.

During data reception, the COM 9032 will convert incoming serial receive data from the transmission media to NRZ form which will directly feed the RX input of the COM 9026 (pin 38). During transmission, the COM 9032 converts the transmit data from the COM 9026 (TX, pin 37) into the waveforms necessary to drive opposite ends of the rf transformer used in the ARCNET\* cable electronics shown in figure 2.

<sup>\*</sup>ARCNET is a registered trademark of the Datapoint Corporation.

230

# **DESCRIPTION OF PIN FUNCTIONS**

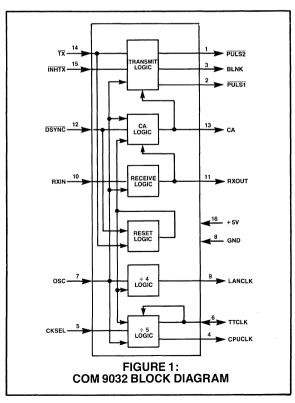

(Refer to figure 2)

#### COM 9026 INTERFACE

| JOIN JULU 1 | NIENI ACE           |                |                                                                                                                                                                                                                                       |

|-------------|---------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NO.     | NAME                | SYMBOL         | FUNCTION                                                                                                                                                                                                                              |

| 1, 2        | PULSE 2<br>PULSE 1  | PULS2<br>PULS1 | PULS2 and PULS1 are two nonoverlapping negative pulses which occur every time the TX input is pulsed. PULS2 and PULS1 are used to feed an external driver as shown in figure 2.                                                       |

| 3           | BLANK               | BLNK           | When used with the circuitry shown in figure 2, this output should be left unconnected. The timing of this signal is shown in figure 4.                                                                                               |

| 10          | RECEIVE IN          | RXIN           | This input is the recovered receive data from the network. For each dipulse appearing on the network, the comparator shown in figure 2 will produce a positive pulse which directly feeds this input.                                 |

| 11          | RECEIVE<br>OUT      | RXOUT          | This output is the NRZ data generated as a function of the RXIN pulse waveform which directly feeds the RX input of the COM 9026 (pin 38).                                                                                            |

| 12          | DELAYED<br>SYNC     | DSYNC          | This active low input, which is asserted by the COM 9026, will halt the CA clock output.                                                                                                                                              |

| 13          | CA                  | CA             | This output is a 5 MHz start/stop clock that is halted when DSYNC goes active low and restarted by a low signal on the RXOUT output. This clock is capable of driving 70 pf plus one LS load with 20 nanoseconds rise and fall times. |

| 14          | TRANSMIT DATA       | TX             | This input, which is asserted by the COM 9026, is the serial data transmitted by the node.                                                                                                                                            |

| 15          | TRANSMIT<br>INHIBIT | INHTX          | This <u>active</u> low <u>input inhibits</u> the TX signal from initiating transmit signals by forcing PULS1 and PULS2 to a high and BLNK to a low. This signal should be asserted during a power on reset condition.                 |

#### SYSTEM CLOCK INTERFACE

| STSTEW CLOCK INTERFACE |                                |                 |                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|------------------------|--------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN NO.                | NAME                           | SYMBOL          | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

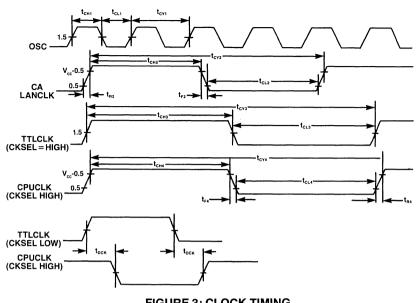

| 4                      | CPU CLOCK                      | CPUCLK          | This output is a 4 MHz free running clock capable of driving 130 pf with 30 nano-<br>second rise and fall times. It is identical to the TTLCLK input when CKSEL is<br>high. When CKSEL is low, this output becomes the inversion of the signal that is<br>fed into the TTLCLK input.                                                                                                                                      |  |  |  |

| 5                      | CLOCK<br>SELECT                | CKSEL           | This input selects the clock interface option for the TTLCLK and CPUCLK. When this signal is high, both the TTLCLK and CPUCLK are identical 4 MHz free running clock outputs which are generated from the 20 MHz input clock (OSC) via a divide by 5 frequency divider. When this input is low, the TTLCLK pin becomes an input and the CPUCLK output will produce the inversion of the signal appearing on TTLCLK input. |  |  |  |

| 6                      | TTL CLOCK                      | TTLCLK          | This pin can be either an input or an output depending on the state of the CKSEL input. When CKSEL is high, a free running 4 MHz clock is ouput. When CKSEL is low, the pin becomes an input which drives an inverter that feeds the CPUCLK output.                                                                                                                                                                       |  |  |  |

| 7                      | OSCILLATOR                     | OSC             | This input requires a 20 MHz clock.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 9                      | LOCAL AREA<br>NETWORK<br>CLOCK | LANCLK          | This output will supply the free running 5 MHz clock to the COM 9026, pin 19. It is capable of driving 70 pf plus one LS load with 20 nanoseconds rise and fall times.                                                                                                                                                                                                                                                    |  |  |  |

| 8                      | GROUND                         | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 16                     | +5 VOLT<br>SUPPLY              | V <sub>cc</sub> | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

#### **FUNCTIONAL DESCRIPTION**

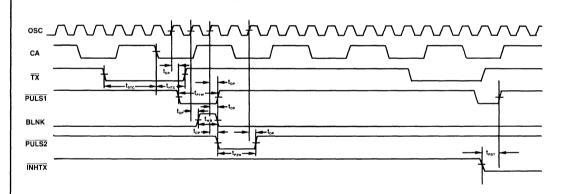

#### Transmit logic (refer to figures 2 and 4)

The COM 9026, when transmitting data on  $\overline{TX}$ , will produce a negative pulse of 200 nanoseconds in duration to indicate a logic "1" and no pulse to indicate a logic "0". Referring to figure 4, a 200 nanosecond pulse on  $\overline{TX}$  is converted to two, 100 nanosecond nonoverlapping pulses shown as PULS1 and PULS2. The signals PULS1 and PULS2 are used to create a 200 nanosecond wide dipulse by driving opposite ends of the RF transformer shown in figure 2.

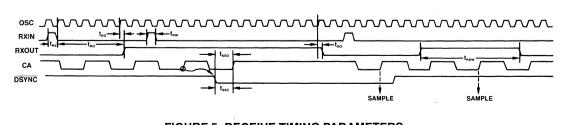

#### Receive logic (refer to figures 2 and 5)

As each dipulse appears on the cable, it is coupled through the RF transformer, passes through the matched filter, and feeds the 75108B comparator. The 75108B pro-

duces a positive pulse for each dipulse received from the cable. These pulses are captured by the COM 9032 and are converted to NRZ data with the NRZ data bit boundaries being delayed by 5 OSC clock periods as shown in figure 5. As each byte is received by the COM 9026, the CA clock is stopped by the COM 9026 (via DSYNC) until the first bit of the next byte is received which will automatically restart the CA clock. The COM 9026 uses the CA clock to sample the NRZ data and these sample points are shown in figure 5.

Typically, RXIN pulses occur at multiples of the transmission rate of 2.5 MHz (400 nanoseconds). The COM 9032 can tolerate distortion of plus or minus 100 nanoseconds and still correctly capture and convert the RXIN pulses to NRZ format.

# **MAXIMUM GUARANTEED RATINGS\***

| Operating Temperature Range           | 0°C to 70°C   |

|---------------------------------------|---------------|

| Storage Temperature Range             | -55° to 150°C |

| Lead Temperature (soldering, 10 sec.) | 325°C         |

| Positive Voltage on any Pin           | + 8V          |

| Negative Voltage on any Pin           |               |

<sup>\*</sup>Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

# DC ELECTRICAL CHARACTERISTICS (T\_A = $0^{\circ}$ C to $+70^{\circ}$ C, $V_{cc}$ = $5V \pm 5\%$ )

| PARAMETER                            | MIN                  | TYP | MAX | UNIT | COMMENTS                                                           |

|--------------------------------------|----------------------|-----|-----|------|--------------------------------------------------------------------|

| INPUT VOLTAGES                       |                      |     |     |      |                                                                    |

| V <sub>IH</sub>                      | 2.7                  |     |     | V    | 1                                                                  |

| V <sub>IL</sub>                      |                      |     | 0.8 | V    |                                                                    |

| OUTPUT VOLTAGES                      |                      |     |     |      |                                                                    |

| $V_{OH1}$                            | 2.4                  |     |     | V    | I <sub>OH</sub> = -0.4 mA, PULS1, PULS2,<br>BLNK, RXOUT and TTLCLK |

|                                      |                      |     |     | į    | outputs.                                                           |

| $V_{OL1}$                            |                      |     | 0.4 | V    | $I_{OL} = 4.0 \text{ mA}, \overline{PULS1}, \overline{PULS2},$     |

|                                      |                      |     | l . |      | BLNK, RXOUT and TTLCLK                                             |

| V                                    | V <sub>cc</sub> -0.5 |     |     | V    | outputs. $I_{OH} = -0.1$ mA, CPUCLK output.                        |

| V <sub>OH2</sub><br>V <sub>OL2</sub> | V <sub>cc</sub> -0.5 |     | 0.4 | V    | I <sub>OI</sub> = 0.1 mA, CPUCLK output.                           |

| V <sub>OH3</sub>                     | V <sub>cc</sub> -0.5 |     | 0.4 | ľ    | $I_{OH} = -0.1 \text{ mA}$ , CA and LANCLK                         |

|                                      | 1                    |     |     |      | outputs.                                                           |

| V <sub>OL3</sub>                     |                      |     | 0.4 | V    | I <sub>oL</sub> = 0.4 mA, CA and LANCLK                            |

|                                      |                      |     | ļ   |      | outputs.                                                           |

| LEAKAGE CURRENT                      |                      |     |     |      |                                                                    |

| 111                                  |                      |     | 50  | μA   | TTLCLK input with CKSEL low.                                       |

| I <sub>12</sub>                      |                      |     | 10  | μΑ   | all other inputs.                                                  |

| INPUT CAPACITANCE                    |                      |     |     |      |                                                                    |

| C <sub>IN</sub>                      |                      |     | 20  | pf   |                                                                    |

| SUPPLY CURRENT                       |                      |     |     |      |                                                                    |

| Icc                                  |                      |     | 20  | mA   | at 20 MHz OSC frequency.                                           |

# **AC CHARACTERISTICS**

| PARAMETER                            | MIN      | TYP                                                        | MAX      | UNIT     | COMMENTS       |

|--------------------------------------|----------|------------------------------------------------------------|----------|----------|----------------|

| OSC Input                            |          |                                                            |          |          |                |

| t <sub>cy1</sub>                     |          | 50                                                         |          | ns       |                |

| t <sub>CH1</sub>                     | 20<br>20 |                                                            |          | ns       |                |

| t <sub>cl1</sub>                     | 20       |                                                            |          | ns       |                |

| CA, LANCLK                           |          |                                                            |          |          |                |

| t <sub>CY2</sub>                     |          | 200                                                        |          | ns       |                |

| CH2                                  | 75<br>75 |                                                            |          | ns       |                |

| t <sub>CL2</sub>                     | /5       |                                                            | 20       | ns<br>ns |                |

| t <sub>F2</sub><br>t <sub>R2</sub>   |          |                                                            | 20<br>20 | ns       |                |

| TTLCLK                               |          |                                                            | 20       | 113      |                |

| TILOLK<br>t                          | *        | 250                                                        |          | ns       |                |

| t <sub>сүз</sub><br>t <sub>снз</sub> | 110      | 250                                                        |          | ns       |                |

| t <sub>CL3</sub>                     | 110      |                                                            |          | ns       |                |

| CPUCLK (CKSEL is high)               |          |                                                            |          |          |                |

| t <sub>CY4</sub>                     |          | 250                                                        |          | ns       |                |

| t <sub>CH4</sub>                     | 110      |                                                            |          | ns       |                |

| t <sub>CL4</sub>                     | 110      | 1 .                                                        |          | ns       |                |

| t <sub>F4</sub> .                    |          |                                                            | 30       | ns       |                |

| t <sub>84</sub>                      |          |                                                            | 30       | ns       | l              |

| t <sub>DCK</sub>                     |          |                                                            | 45       | ns       | for CKSEL low. |

| TRANSMIT TIMING                      |          |                                                            |          | 1        |                |

| t <sub>stc</sub>                     | 50<br>10 | 30                                                         |          | ns       |                |

| <b>t</b> нтс                         | 10       |                                                            |          | ns       |                |

| t <sub>DP</sub>                      |          | 2+                                                         | 60       | ns<br>ns |                |

| t <sub>P1W</sub><br>t <sub>wB</sub>  |          | 2t <sub>CY1</sub><br>t <sub>CY1</sub><br>2t <sub>CY1</sub> |          | ns       |                |

| t <sub>P2W</sub>                     |          | 2t-                                                        |          | ns       |                |

| t <sub>RST</sub>                     |          | L-CY1                                                      | 40       | ns       |                |

| RECEIVE TIMING                       |          |                                                            |          |          |                |

| t <sub>RS</sub>                      | 30       |                                                            |          | ns       |                |

| t <sub>RW</sub>                      | 30<br>10 |                                                            |          | ns       |                |

| t <sub>po</sub>                      |          |                                                            | 70       | ns       |                |

| t <sub>RO</sub>                      |          | $5t_{CY1} + t_{DO}$                                        |          | ns       |                |

| t <sub>sso</sub>                     | 10       |                                                            |          | ns       |                |

| t <sub>ssc</sub>                     |          | 20                                                         |          | ns       |                |

| t <sub>ROW</sub>                     |          | 400                                                        |          | ns       |                |

FIGURE 3: CLOCK TIMING

FIGURE 4: TRANSMIT TIMING PARAMETERS

FIGURE 5: RECEIVE TIMING PARAMETERS

Circuit diagrams utilizing SMC products are included as a means of illustrating typical semiconductor applications; consequently complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of SMC or others. SMC reserves the right to make changes at any time in order to improve design and supply the best product possible.