## jr2ndMATE

# INSTALLATION MANUAL

#### **TECMAR INCORPORATED**

6225 Cochran Road Solon, Ohio 44139-3377

Telex: 466692

Copyright 1984 by Tecmar, Inc.

#931681 Rev. A

**Printed by Tecmar Presses**

### **Limited Warranty**

Tecmar, Inc. ('Tecmar') warrants to the **original purchaser** that boards and cables manufactured by Tecmar will be free from defects in materials and workmanship for one year from the date of delivery to purchaser. Tecmar warrants to the **original purchaser** that disc controllers and drives, terminals, printers, and any other non-board item not bearing a Tecmar label will be free from defects in materials and workmanship for a period of ninety days from the date of delivery to purchaser. Tecmar warrants to the **original purchaser** that the media for software will be free from defects in materials and will be readable by the computer system for a period of ninety days from the date of delivery to purchaser. The software is thoroughly tested and thought to be functional when released; at Tecmar's sole option, Tecmar may endeavor to correct any serious problems discovered in the software.

Under the above warranty, Tecmar will, at its option, either repair or replace a non-conforming or defective product, or return to purchaser the purchase price. Tecmar shall have no obligation hereunder if the product has been misused, carelessly handled, defaced (including unauthorized repairs made or attempted by others), modified or altered. The product must be returned with proof of purchase in its original (or other adequate packaging) to the point of purchase or, by prior arrangements with Tecmar, to Tecmar. Claims must be made in accordance with the provisions of this paragraph within the applicable warranty period or they will be barred.

Tecmar reserves the ultimate authority to determine what constitutes warranty repair. If it is determined that the product is not under warranty, it will be repaired using Tecmar's standard rates for parts and labor. Tecmar will use its best efforts to repair the product within three days after receipt thereof. Tecmar shall not be responsible, however, for delays caused by shipping of non-availability of replacement components or other similar or dissimilar causes, events or conditions beyond its reasonable control.

The above warranty is the only warranty authorized by Tecmar. THE ABOVE WARRANTY STATES THE PURCHASER'S EXCLUSIVE REMEDY FOR ANY BREACH OF TECMAR'S WARRANTY AND FOR ANY CLAIM, WHETHER SOUINDING IN CONTRACT, TORT OR NEGLIGENCE, FOR LOSS OR INJURY CAUSED BY THE SALE OF ANY PRODUCT. WITHOUT LIMITING THE GENERALITY OF THE FOREGOING, TECMAR SHALL IN NO EVENT BE RESPONSIBLE FOR ANY LOSS OF BUSINESS OR PROFITS, DOWNTIME OR DELAY, LABOR, REPAIR, OR MATERIAL COSTS, INJURY TO PERSON OR PROPERTY OR ANY SIMILAR OR DISSIMILAR CONSEQUENTIAL LOSS OR DAMAGE INCURRED BY PURCHASER, EVEN IF TECMAR HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH LOSSES OR DAMAGES.

SOME STATES DO NOT ALLOW THE EXCLUSION OR LIMITATION OF INCIDENTAL OR CON-SEQUENTIAL DAMAGES OR LIMITATIONS ON HOW LONG AN IMPLIED WARRANTY LASTS, SO THE ABOVE LIMITATION OR EXCLUSION MAY NOT APPLY TO YOU.

THIS WARRANTY SHALL NOT BE APPLICABLE TO THE EXTENT THAT ANY PROVISION OF THIS WARRANTY IS PROHIBITED BY ANY FEDERAL, STATE OR MUNICIPAL LAW WHICH CANNOT BE PREEMPTED. THIS WARRANTY GIVES YOU SPECIFIC LEGAL RIGHTS, AND YOU MAY ALSO HAVE OTHER RIGHTS WHICH VARY FROM STATE TO STATE.

| Keep your original sales receipt for | the product with this warranty statement. |

|--------------------------------------|-------------------------------------------|

| PRODUCT                              |                                           |

| Serial<br>Number                     | DATE OF PURCHASE                          |

| WHERE<br>PURCHASED                   |                                           |

### **Contents**

|                                       | Page No |

|---------------------------------------|---------|

| Checklist                             | . 1     |

| Section 1.  jr2ndMATE Installation    | . 3     |

| -                                     |         |

| Installation Requirements             | . 7     |

| Tools Required                        | . 7     |

| Installation Instructions             | . 7     |

| Section 2.                            |         |

| <i>jr</i> 2ndMATE Technical Reference | . 15    |

| Jumper Blocks                         | . 19    |

| The $jr$ 2ndMATE's Jumper Blocks .    | . 20    |

| I/O Configuration                     | . 23    |

| The Parallel Printer Port             | . 24    |

| I/O Address 378                       | . 25    |

| I/O Address 379                       |         |

| I/O Address 37A                       |         |

| Parallel Port Pin Out                 | . 26    |

| The Time of Day Chip                  | . 27    |

| I/O Addresses                         |         |

| Counters and Latches                  |         |

| Interrupt Control Register            |         |

| Interrupt Status Register             |         |

| Counter Reset Register                |         |

| Latch Reset Register                  |         |

| Rollover Bit Register                 |         |

| Go Register                           | . 33    |

| Appendix A:                           |         |

| Specifications                        | . A1    |

| Appendix B:                           |         |

| Block Diagram Description             | R1      |

## FEDERAL COMMUNICATIONS COMMISSION RADIO FREQUENCY INTERFERENCE STATEMENT

**Warning:** This equipment has been certified to comply with the limits for a Class B computing device, pursuant to Subpart J of Part 15 of FCC rules. Only peripherals cesigned to operate on the PCjr Bus and certified to comply with the Class B limits may be attached to this peripheral. Operation with non-certified peripherals is likely to result in interference to radio and TV reception.

## FCC Required Instructions to IBM PCjr User

This equipment generates and uses radio frequency energy and if not installed and used properly, i.e., in strict accordance with the operating instructions, reference manuals, and the service manual, may cause interference to radio or television reception. It has been tested and found to comply with the limits for a Class B computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a residential installation.

If this equipment does cause interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient the receiving antenna.

- Relocate the equipment with respect to the receiver.

- · Move the equipment away from the receiver.

- Plug the equipment into a different outlet so that equipment and receiver are on different branch circuits.

If necessary, the user should consult the dealer or an experienced radio/television technician for additional suggestions. The user may find the following booklet prepared by a the Federal Communications Commission helpful:

"How to Identify and Resolve Radio-TV Interference Problems".

This booklet is available from the U.S. Government Printing Office, Washington, DC 20402, Stock No. 004-000-00345-4.

The manufacturer is not responsible for any radio or TV interference caused by unauthorized modifications to this equipment. It is the responsibility of the user to correct such interference.

# Your IBM PCjr should be set up before installing jr2ndMATE. Refer to your IBM Guide to Operations to perform this task.

This carton contains the following:

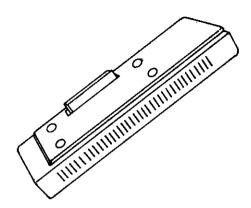

jr2ndMATE

Four Mounting Screws

• One Software Diskette

- Installation Manual

- Software Manual

If any items are missing or damaged, notify your place of purchase.

Lay the four mounting screws aside. You will use them later to attach the *jr*2ndMATE to the IBM PC*jr*.

# Section 1. jr2ndMATE Installation

### Contents

| nstallation Requirements | 7 |

|--------------------------|---|

| Tools Required           | 7 |

| nstallation Instructions | ; |

#### **Installation Requirements**

If your IBM PCjr has not been set up at this time, do so before installing the jr2ndMATE. Your computer must have:

· One disk drive

#### **Tools Required**

· Medium-size, flat-blade screwdriver.

#### **Installation Instructions**

1. Turn your IBM PCjr power off.

**Warning:** After turning your IBM PC*jr* power off, allow five minutes for cooling to take place before removing the option attachment cover.

- 2. Turn power off on everything attached to your IBM PCjr (printers, television, etc.).

- Unplug your IBM PCjr and your display or television power cords from the wall outlets.

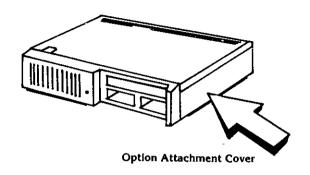

Face the front of the computer system. In order to install the jr2ndMATE you must first remove the option attachment cover on the right hand side of the computer sytem.

**Note:** *jr*2ndMATE can be installed on the side of the PC*jr* or on the side of another Tecmar product.

5. Remove the option attachment cover by gently pulling until it snaps out of place.

- 6. The option attachment cover should be put aside. You will attach it to the side of the installed *jr*2ndMATE in step 10.

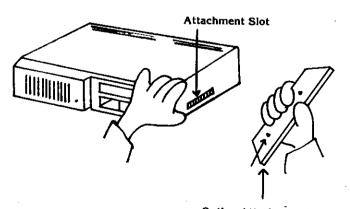

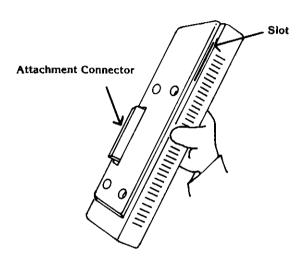

- 7. Pick up the *jr*2ndMATE. Hold it as shown in the picture.

Jr2ndMATE

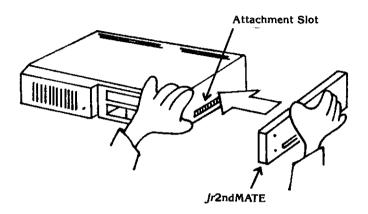

8. Locate the attachment slot on the right side of the IBM PCjr. Plug the attachment connector of the jr2ndMATE into the attachment slot at the side of the IBM PCjr.

9. Is the jr2ndMATE firmly in place and evenly lined up with the side of the IBM PCjr?

Yes - go to step 10.

No - go to step 8.

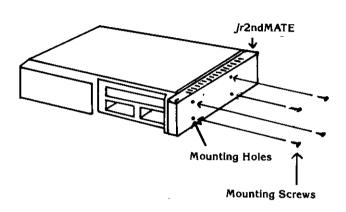

10. Secure the jr2ndMATE to the side of the IBM PCjr using the four mounting screws you put aside. Reinstall the option attachment cover by pressing it firmly into the mounting holes of the jr2ndMATE.

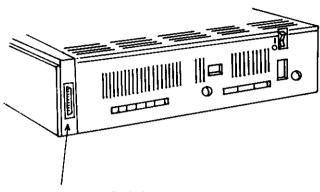

11. Turn your IBM PCjr so the back is toward you.

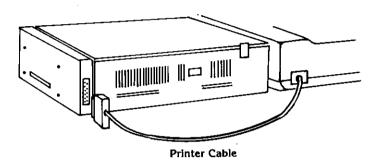

12. Look at the back of the *jr*2ndMATE. Find the Graphics Printer Socket.

Graphics Printer Socket

13. Plug the cable coming from your printer into the graphics printer socket on the back of the *jr*2ndMATE.

**Note:** You must use a shielded cable to connect your printer to the computer in order to comply with FCC regulations.

14. Turn your IBM PCjr to the desired position for use.

### Section 2. jr2ndMATE Technical Reference

This technical reference section is here for your information as it is needed. You do not have to read this section to use the *jr*2ndMATE.

#### **Contents**

| Jumper Blocks19                          |

|------------------------------------------|

| I/O Configuration23                      |

| The Parallel Printer Port24              |

| The Time of Day Chip27                   |

| Appendix A: Specifications               |

| Appendix B: Block Diagram Description B1 |

#### Jumper Blocks

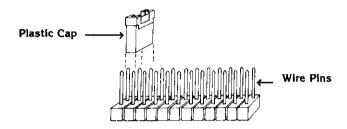

The jumper block is a plastic block with perpendicular wire pins protruding from its top surface. Positions in this jumper block are connected by placing a plastic cap over two adjacent pins. The two pins represent one position on the jumper block.

To disconnect a position, remove the plastic cap by hand or with a pair of tweezers or needle-nose pliers.

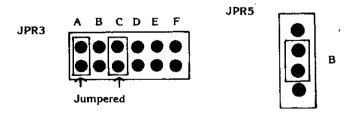

When the plastic cap is in place, a connection has been made and that position is jumpered. In the diagrams below, Jumper Block JPR3 is jumpered in positions A and C and Jumper Block JPR5 is jumpered in position B.

**Note:** The jumper blocks shown above are examples only. They do not appear on your *jr*2ndMATE board.

#### The jr2ndMATE's Jumper Blocks

#### Jumper 1

Jumper 1 selects the I/O address port that addresses the parallel port and the time of day chip.

When jumpered in the left position,

the printer port is addressed through addresses 378, 379, and 37A. The time of day is addressed through addresses 37D and 37F. When Jumper 2 is jumpered in the left position, the printer port address is referred to as LPT1, while the time of day port address is referred to as TIME1.

When jumpered in the right position,

the printer port is addressed through addresses 278, 279, and 27A. The time of day is addressed through addresses 27D and 27F. When jumper 1 is jumpered in the right position, the printer port address is referred to as LPT2, while the time of day port address is referred to as TIME2.

More specific information about jumper 1 can be found in the I/O Configuration discussion in this section.

Note:

Jumper 1 is normally jumpered as LPT1 and TIME1. If you already have a *jr*2ndMATE or a *jr*Captain installed in your IBM PC*jr* addressed as LPT1 and TIME1, leave this jumper off or place the jumper in the right position to jumper your *jr*2ndMATE as LPT2 and TIME2.

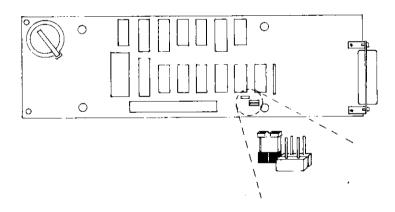

The picture below shows the location of jumper 1 and jumper 2 on your *jr*2ndMATE board.

#### Jumper 2

Jumper 2 selects the interrupt line on which an interrupt may be generated from the time of day chip.

If jumper 2 is not jumpered,

no interrupt is generated.

If jumper 2 is jumpered in the low position,

an interrupt may be generated on IRQ1.

If jumper 2 is jumpered in the high position,

an interrupt may be generated on IRQ2.

#### I/O Configuration

As mentioned previously, the I/O addresses used for the parallel port and time of day chip may be selected by jumper 1.

When jumper 1 is jumpered in the left position, the following applies.

| Address                                                     | Function       | Read/<br>Write  | None  |

|-------------------------------------------------------------|----------------|-----------------|-------|

| 888 Dec (378 Hex)<br>889 Dec (379 Hex)<br>890 Dec (37A Hex) | Printer Status | R/W<br>R<br>R/W | LPT1  |

| 893 Dec (37D Hex)<br>895 Dec (37F Hex)                      | latch          | W<br>R/W        | TIME1 |

When jumper 1 is jumpered in the right position, the following applies.

| Address           | Function               | Read/<br>Write | None  |

|-------------------|------------------------|----------------|-------|

| 632 Dec (278 Hex) | Printer Data           | R/W            |       |

| 633 Dec (279 Hex) | Printer Status         | R              | LPT2  |

| 634 Dec (27A Hex) | Printer Control        | R/W            |       |

| 637 Dec (27D Hex) | Clock Address<br>latch | W              | TIME2 |

| 639 Dec (27F Hex) | Clock data             | R/W            |       |

In this manual, most examples assume that the *jr*2ndMATE board is configured as TIME1 and LPT1. If your board is addressed differently, use the corresponding addresses.

#### The Parallel Printer Port

The printer port on the *jr*2ndMATE has a parallel interface which allows it to be easily used with an IBM printer or an EPSON MX80 or RX80. It is directly compatible with the parallel port provided for the IBM PC and may be accessed using IBM software. It may also be used as a general parallel port for input and output.

There are three I/O addresses associated with the parallel printer port. Depending on how jumper 1 is jumpered, the addresses are 378, 379 and 37A or, 278, 279 and 27A. For this description, we will assume that jumper 1 has been jumpered in the left position so that the addresses used are 378, 379 and 37A.

#### I/O Address 378 (printer data)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

The eight bit value written to this port address appears on the eight data pins of the parallel printer port. If this port is read, the last value that was written to this port is returned.

#### I/O Address 379 (printer status)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  |

|-------|-------|-------|-------|-------|--------|--------|--------|

| BUSY  | ACK   | PE    | SEL   | ERROR | Unused | Unused | Unused |

This port address is read only and may not be written to. The value read is the current value of the above pins.

#### I/O Address 37A (printer control)

| Bit 7  | Bit 6  | Bit 5 | Bit 4               | Bit 3 | Bit 2 | Bit 1        | Bit 0  |

|--------|--------|-------|---------------------|-------|-------|--------------|--------|

| Unused | Unused |       | INTERRUPT<br>ENABLE |       |       | AUTO<br>FEED | STROBE |

This port address may be written to set the value of any of the above pins. You may also read the port address to get the current value of the above pins.

#### Parallel Port Pin Out

The parallel port has 12 buffered output pins which are latched and can be written to or read from at any time. There are 5 steady state input pins which may be read at any time. The other 8 pins are unused.

The pin out of the parallel port is given below.

| Pin | Signal Name                | Description    |

|-----|----------------------------|----------------|

| 1   | -STROBE                    | Strobe         |

| 2   | D0                         | Data bit 0     |

| 3   | D1                         | Data bit 1     |

| 4   | D2                         | Data bit 2     |

| 5   | D3                         | Data bit 3     |

| 6   | D4                         | Data bit 4     |

| 7   | D5                         | Data bit 5     |

| 8   | D6                         | Data bit 6     |

| 9   | D7                         | Data bit 7     |

| 10  | – ACK                      | Acknowledge    |

| 11  | +BUSY                      | Busy           |

| 12  | +PE                        | Parity enable  |

| 13  | +SEL                       | Select         |

| 14  | <ul><li>AUTOFEED</li></ul> | Automatic feed |

| 15  | ERROR                      | Error          |

| 16  | – INIT                     | Initialize     |

| 17  | SELINP                     | Select input   |

| 18  | GROUND                     | Unused         |

| 19  | GROUND                     | Unused         |

| 20  | GROUND                     | Unused         |

| 21  | GROUND                     | Unused         |

| 22  | GROUND                     | Unused         |

| 23  | GROUND                     | Unused         |

| 24  | GROUND                     | Unused         |

| 25  | GROUND                     | Unused         |

#### The Time Of Day Chip

The time of day chip keeps track of the current time and date. Because it is powered by its own battery, it will still remember the time when the *jr*2ndMATE is turned off. The chip may also be used to cause an interrupt when the current time and date match a previously set time and date.

There are two I/O addresses associated with the time of day chip. Depending on how jumper 2 is jumpered, the addresses are 37D and 37F or the addresses 27D and 27F. For this description, we will assume that jumper 2 has been jumpered to the high position so the addresses used are 37D and 37F.

#### **Replacing Your Battery**

The battery for the clock/calendar on your *jr*Captain may need to be replaced once each year. Return your *jr*Captain to your dealer or to Tecmar for a replacement.

The battery must be replaced by a factory trained technician.

#### I/O Addresses

There are 22 registers inside the time of day chip. Each of the registers is 8 bits wide. There are 16 read/write registers, 2 read/only registers and 4 write/only registers. They are described in the following chart.

| Address | Access | Function                           |

|---------|--------|------------------------------------|

| 0       | R/W    | Thousandth second counter          |

| 1       | R/W    | Tenth and hundredth second counter |

| 2       | R/W    | Second counter                     |

| 3       | R/W    | Minute counter                     |

| 4       | R/W    | Hour counter                       |

| 5       | R/W    | Day of the week counter            |

| 6       | R/W    | Day of the month counter           |

| 7       | R/W    | Month counter                      |

| 8       | R/W    | Thousandth second latch            |

| 9       | R/W    | Tenth and hundredth second latch   |

| 10      | R/W    | Second latch                       |

| 11      | R/W    | Minute latch                       |

| 12      | R/W    | Hour latch                         |

| 13      | R/W    | Day of the week latch              |

| 14      | R/W    | Day of the month latch             |

| 15      | R/W    | Month latch                        |

| 16      | R      | Interrupt status register          |

| 17      | W      | interrupt control register         |

| 18      | W      | Counter reset                      |

| 19      | W      | Latch reset                        |

| 20      | R      | Rollover bit                       |

| 21      | W      | Go register                        |

To read or write to one of the 22 registers in the time of day chip, first write the value of it's address to I/O address 37D. The address will be a number between 0 and 21. Then, by reading or writing to I/O address 37F, you will read or write the corresponding register in the time of day chip.

#### Counters and Latches

All of the values for the counter or latch registers in the time of day chip are encoded in BCD or binary coded decimal. In BCD, an 8 bit byte is divided into 2 nibbles, each of which is 4 bits in length. Each nibble may contain a value between 0 and 9. These two numbers are put together to form the decimal number. For example, the decimal number 27 is represented by the BCD binary number 0010 0111. The high order nibble is the 2 and the low order nibble is the 7. This number is 27 in hexadecimal or 39 in decimal. Thus the decimal number 27 when converted to BCD becomes the decimal number 39.

The thousandths of second register contains a value from 0 to 9. The tenth and hundredth of second register contains a value from 0 to 99. The second register and minute registers contain a value from 0 to 59. The hour register uses the 24 hour clock. Midnight is represented by 0 while 11 p.m. is represented by 23. The day of the week register contains a value from 1 to 7. Sunday is represented by 1 while Saturday is represented by 7. The day of the month register contains a value from 1 to 31. The month register contains a value between 1 and 12. January is represented by 1 while December is represented by 12. Remember that these values are stored in BCD.

#### **Interrupt Status Register**

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1              | Bit 0          |

|-------|-------|-------|-------|--------|--------|--------------------|----------------|

| month | week  | day   | hour  | minute | second | tenth of<br>second | latch<br>alarm |

This register is used to determine the source of an interrupt. When an event occurs that would trigger an interrupt, the corresponding bit will be set in this register. Reading this register will clear it.

Note that the interrupt status register will contain valid information whether or not the board has been jumpered for interrupts. This allows you to use a board that has not been jumpered for interrupts as a timer. Rather than having an interrupt routine, you must poll the interrupt status register until one of the bits is set.

#### Interrupt Control Register

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1              | Bit 0 |

|-------|-------|-------|-------|--------|--------|--------------------|-------|

| month | week  | day   | hour  | minute | second | tenth of<br>second |       |

By setting any one of the bits from 1 to 7, you may cause an interrupt to be generated when the corresponding counter rolls over to it's minimum value. If more than one bit has been set, the lowest order bit takes effect. Note that the board must be jumpered for interrupts in order for the interrupt to be generated.

If bit 0 is set, an interrupt will be generated when the values of each of the counter registers match the corresponding values of each of the latch registers.

#### Counter Reset Register

You may set all the counter registers to their minimum values by writing a hexadecimal FF to this register.

#### atch Reset Register

All the latch registers may be set to their minimum values by writing a hexadecimal FF to this register.

#### Rollover Bit Register

This register is set to 1 anytime any of the counters change their value. As the thousandths second counter is set every thousandth of a second, this register is set to 1 at that rate. Reading this register will clear it.

Before reading the counters, you should read the rollover bit register to clear it. Read all the counter registers you wish to read and then read the rollover bit register again. If the rollover bit register has been set, you must go through this operation again.

The reason that the above procedure should be followed is that should the time of day chip be in the process of updating the counters while you are reading them, you may get some of the old values and some of the new values. This could result in an incorrect time.

#### Go Register

If a 1 is written to this register, the thousandths second counter and the tenth and hundredth second counter is reset. The purpose of this register is to allow you to set the other counter registers, wait until the thousandth second counter and the tenth and hundredths second counter should be zero before setting this register to 1.

The reason for setting the time in this way is that it may take a longer time to set the thousandths second counter and the tenth and hundredth second counter than it takes for those counters to update. Using the above procedure allows the time to be set very quickly.

# Appendix A: Specifications

Parallel Printer Port

I/O Address:

Jumper selectable between the addresses 378, 379, 37A and the addresses 278, 279, 27A.

Clock/Calendar

I/O Address:

Jumper selectable between the addresses 37D and

37F and the addresses

27D and 27F.

Load:

1 TTL load/bus line max.

Battery Life:

Approximately one year.

Not user replaceable.

Power:

400 mA @ +5V max

280 mA @ +5V typ

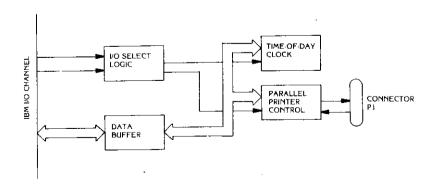

# Appendix B: Block Diagram Description

- 1. **Data buffer:** A bidirectional buffer transfers data between the IBM data lines and I/O sections on the board.

- I/O select logic: When the address is correct, this section selects one of the I/O sections for I/O read or write operations.

- Time of day clock: The real-time clock is made up of an address latch, the clock itself (MM58167) and the battery for standby power.

- 4. Parallel printer port: The printer port is completely compatible with all IBM software and is meant to connect to an IBM, EPSON, or equivalent printer. The parallel printer port is available through connector P1.

| // ZIIQ/ 1/11 L | dMATE |

|-----------------|-------|

|-----------------|-------|

20501

Your comments are a vital tool in assisting us in our efforts to continue the improvement of PC-Mate products and the accompanying manuals.

Suggestions may be used or distributed by Tecmar in any form it believes appropriate without any obligation whatever. This does not limit your use of the information that you originate and supply to Tecmar.

Comments:

| Name     |       |

|----------|-------|

| Address  |       |

| City     | State |

| 7in Codo |       |

### **TECMAR INCORPORATED**

PERSONAL COMPUTER PRODUCTS DIVISION 6225 COCHRAN ROAD SOLON, OHIO 44139-3377 TELEX: 466692